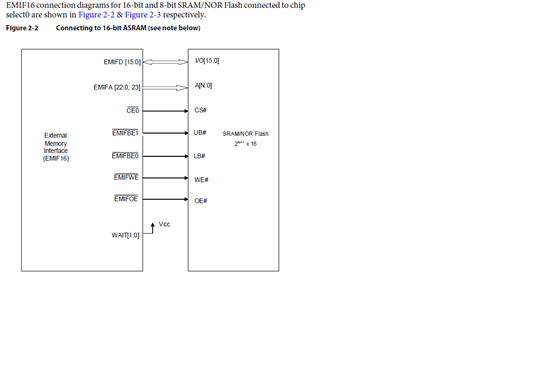

Another post relating to connecting an FPGA to a C6678 over EMIF-16. The Keystone EMIF docs (SPRUGZ3A) show several different ways of configuring the interface, eg. for NAND flash versus NOR flash.

We reasoned that our FPGA was most like NOR flash/ASRAM and started working from Fig 2.2 (p2-4) which show the address lines A[23:0] being wired to NOR device address lines as A[22:0, 23]. There is a note which says

"Note—EMIFA[23:22] behave as address selects. For 16-bit interface, EMIFA23

is connected to address pin A0 of the ASRAM/NOR Flash. For 8-bit interface,

EMIFA[23:22] are connected to address pins A[1:0] of the ASRAM/NOR

Flash."

Except, in our case this doesn't seem to make sense - the address seems to come out "naturally" on A[23:0] without this rearrangement.

So my question is, what is this A[22:0, 23] business about? I could understand shifting the address right to omit the irrelevant bit 0, but why shift left and what does A23 have to do with things? Is there some NOR-flash mode that we should or should not be enabling in order to use the address bus sensibly?

Thanks in advance,

Gordon