boot core1 using core0 on TMDXEVM6678LE,code is following:

#define IPCGR_REG ((volatile unsigned int*)0x02620240)

unsigned int magic=0x1187fffc;

if(0 == corenum)

{

memcpy((void*)(0x11800000), (void*)0x00800000, 512*1024);

// 0x1186d800 is the address of _c_int00 for core1 that caculated via _c_int00 address in .map file

*((volatile unsigned int*)magic) = 0x1186d800 ;

// Initialize main Platform lib

memset(&init_config, 0, sizeof(platform_init_config));

memset(&init_flags, 1, sizeof(platform_init_flags));

if (platform_init(&init_flags, &init_config) != Platform_EOK)

{

printf ("Platform init failed!\n");

print_platform_errno();

return;

}

platform_uart_init();

platform_uart_set_baudrate(BOOT_UART_BAUDRATE);

/* sent IPC interrupt to core1 */

IPCGR_REG[1] = 1;

while(1)

{

for (i=0; i< 100000000; i++) ;

write_uart(core_msg0);

}

}

else if(1 == corenum)

{

while(1)

{

for (i=0; i< 100000000; i++) ;

write_uart(core_msg1);

}

}

Question:

(1)0x1186d800 in the code is the address for _c_int00 in .map file add 0x1100000, is it right ?

(2)when the code is loaded into core0 and run core0,it can print right message through UART, and I check the L2 of core1,the code is copied into L2 of core1.

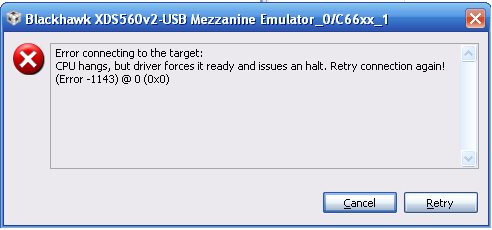

(3)when the code is loaded into core0 and run core0,I check L2 via core1 ,the message is following,is it means core1 is interrupted by IPC ?

(4)when i check IPCGR_REG[1],value is 0. IPCGR_REG[1] is cleared after IPCGR_REG[1] is set 1 itself,is it right?

(5)why core1 can not be boot?