This is regarding the ARM view and DSP view of DDR3A and DDR3B. It is still not clear after going through the below post on DDR3A and DDR3B mapping and ARM and DSP view.

http://e2e.ti.com/support/dsp/c6000_multi-core_dsps/f/639/p/300548/1058399.aspx#1058399

The XTCIEVMK2X Rev1.0 is mounted with 2GB DDR3 DIMM as DDR3A and 1GB of DDR3B.

My questions are:

1. U-Boot detects only 1GB of DDR3, is that DDR3A or DDR3B??

If it is DDR3A, why it shows only 1GB?

U-Boot SPL 2013.01-dirty (Nov 25 2013 - 11:19:53)

SF: Detected N25Q128A with page size 64 KiB, total 16 MiB

U-Boot 2013.01-dirty (Nov 25 2013 - 11:19:53)

I2C: ready

Detected SO-DIMM [ǧSQR-SD3T-2G1333]

DRAM: 1 GiB

NAND: 512 MiB

Net: TCI6638_EMAC, TCI6638_EMAC1

Hit any key to stop autoboot: 0

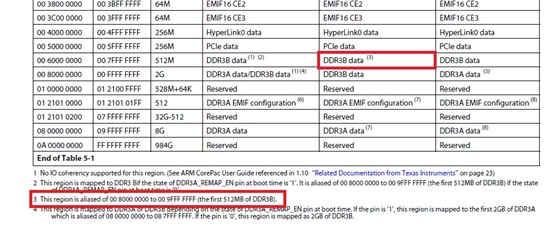

2. From the datasheet, page number 94, SPRS866E November 2013,

Let us first assume the scenario where DDR3A_REMAP_EN pin is '0' which is default settings in the EVM,

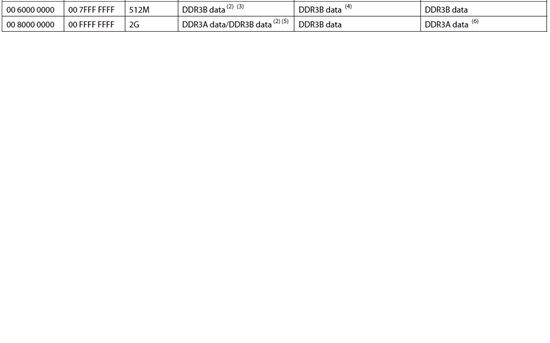

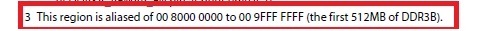

The physical memory 00 6000 0000 to 00 7ffff ffff (512M) from ARM view refers to DDR3B data which is same as that of 00 8000 0000 to 00 9ffff ffff as this is aliased of 00 8000 0000 to 00 9ffff ffff (the first 512MB of DDR3B)

The physical memory 00 8000 0000 to 00 FFFF FFFF (2G) from ARM view will be DDR3B data as DDR3A_REMAP_EN pin is '0'. DSP view will be DDR3B data.

The kernel load address and u-boot CONFIG_SYS_SDRAM_BASE points to 0x80000000

Therefore, in this case, does that mean the EVM uses only DDR3B for both ARM and DSP?

2. Given the DDR3A and DDR3B sizes for EVM, it would be nice to know the ARM view and DSP view of address ranges, with and without DDR3A_REMAP_EN pin enabled.

Target chip : TCI6638k2k

Target EVM : XTCIEVMK2X Rev1.0

CCS ver : CCS 5.4.0.00091

MCSDK version:

mcsdk_bios_3_00_01_12

mcsdk_linux_3_00_01_12