Hi,

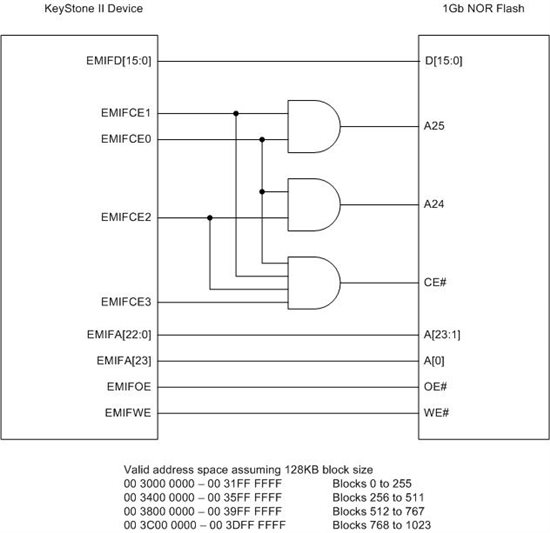

Our aim is to connect 128MB x16 NOR flash to EMIF-16 interface.

1. Can you please let us know what is the maximum size of 16bit NOR flash that can be interfaced through EMIF-16 interface in Keystone 2?

2. As per the documentation, SPRS866E, page no. 93 says that EMIF 16 supports 64M per CE.

00 3000 0000 - 00 33FF FFFF 64M EMIF16 CE0 EMIF16 CE0 EMIF16 CE0

00 3400 0000 - 00 37FF FFFF 64M EMIF16 CE1 EMIF16 CE1 EMIF16 CE1

00 3800 0000 - 00 3BFF FFFF 64M EMIF16 CE2 EMIF16 CE2 EMIF16 CE2

00 3C00 0000 - 00 3FFF FFFF 64M EMIF16 CE3 EMIF16 CE3 EMIF16 CE3

How can we then interface 128MB flash with 24 EMIF address lines and together with CE0 & CE1?

Thanks

Rams