Hi,

I have yet another problem in using the EDMA3 in the C6638 K2H EVM board rev 4.0.

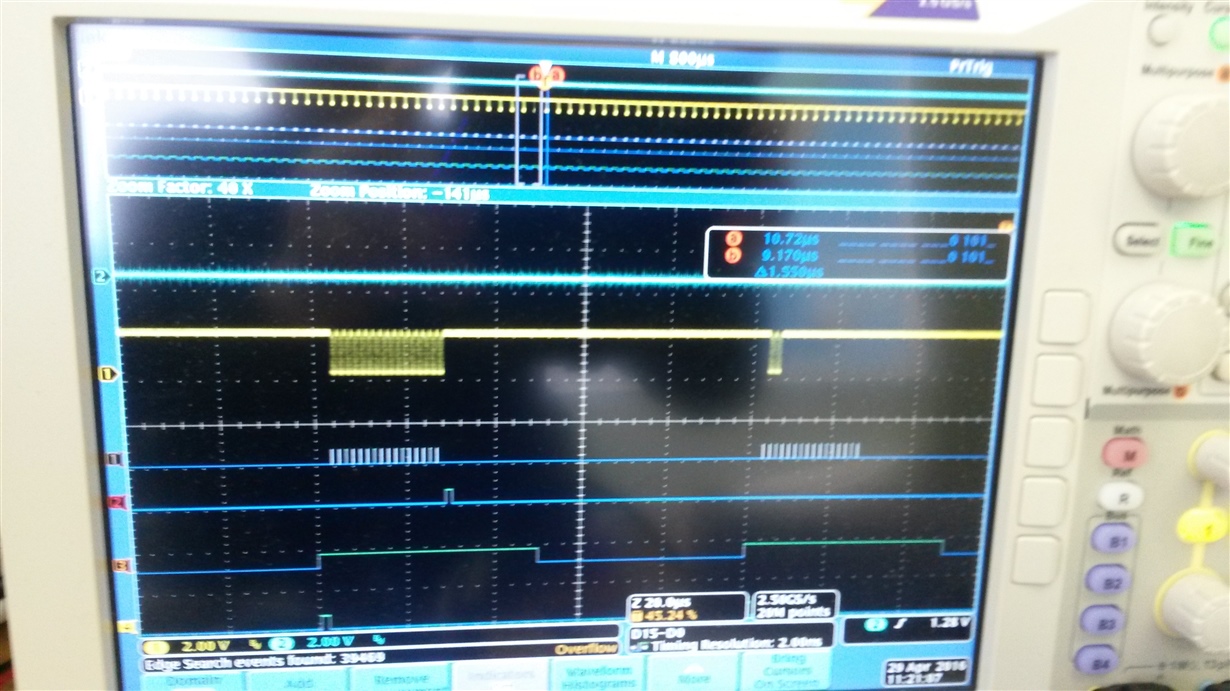

I use the GPIO8 as the synchronization event for the DMA transfers but every time I enable the channel either by writing into the EESR register or by calling the "EDMA3_DRV_enableTransfer()", the transfer immediately begins regardless of the electrical state of the GPIO8 pin.

I guess there is a C66 CorePac event (or interrupt) register which I should clear before enabling the event, but so far have not found such a register with the emulator or from numerous forums and specifications.

I have checked the EVM board schematics to see if there is some circuit driving the GPIO8 pin but I could not find anything different to the other pins (like GPIO10) which I use as an interrupt source for another purpose at the same time without any problems. Also, I cannot see anything happening in the pin with an oscilloscope or in the GPIO "data in" register.

When triggering the GPIO8 EDMA input event manually in the software by writing into the ESR register, it works perfectly without any problems, but not with an external source like already mentioned above.

I have not specified any event combiner or interrupt service routine for the GPIO8 because I want to use it only as a EDMA input without interrupting the CPU with it. So I think I should do some event clearing like in an interrupt handler, but just don't know in details how.

Best regards,

Ari