Hello everyone:

I have a customized board, ipnc_psp_arago package 04.04.00.02 on DM385 platform.

I want test on LCD display color bar, my LCD is connect to DVO2, 8bit line : VOUT0_G_Y_YC[2] ~VOUT0_G_Y_YC[9]

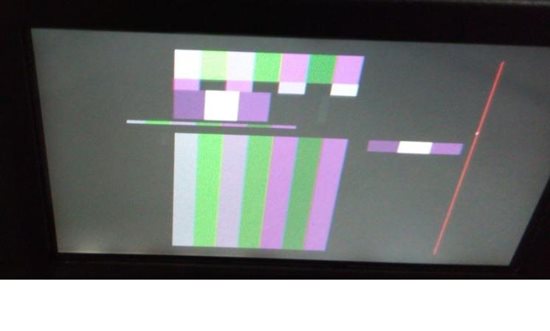

480i color bar display

The color is wrong, could expert can help me? or any suggest.

my config value please refer below. Thank you very much.

--------------------------------------------------------------------------------------

LCD spec :

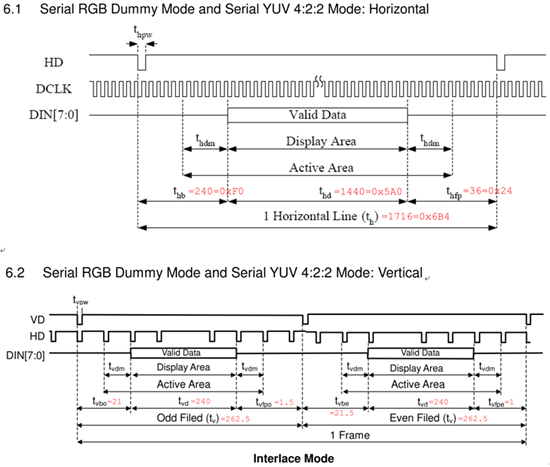

its work on YUV 4:2:2, Interlace Mode

Number of Dots (HxV) 960 x 240 Dot

Horizontal:

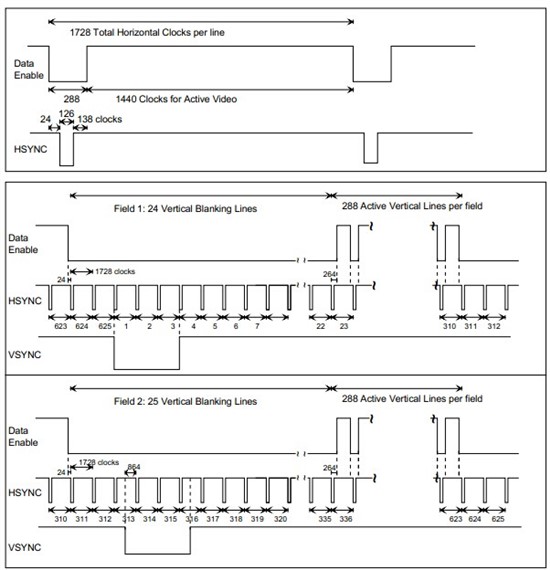

ITUR601-NTSC Timing:

CLK 27 Mhz,

Horizontal Display Active 1440 CLK

Horizontal Line 1716 CLK

HSYNC Pulse Width 1 CLK

Horizontal Back Porch 240 CLK

Horizontal Front Porch 36 CLK

Horizontal Dummy Time 4 CLK

Vertical:

Vertical Display Active 240 Line

Vertical Total Time 262.5 Line

VSYNC Pulse Width 1 CLK

Vertical Back Porch

1. Odd Field 21 Line

2. Even Field 21.5 Line

Vertical Front Porch

1. Odd Field 1.5 Line

2. Even Field 1 Line

Vertical Dummy Time 0 Line

Latch data edge : Positive Edge

HD Polarity : Low pulse

VD Polarity : Low pulse

YcbCr se-quence : CbYCrY

--------------------------------------------------------------------------------------

DVO2 cfg register value

/usr/bin/mem_rdwr.out --wr 0x4810A004 003F0275

/usr/bin/mem_rdwr.out --wr 0x4810A008 1EA500BB

/usr/bin/mem_rdwr.out --wr 0x4810A00c 1F9901C2

/usr/bin/mem_rdwr.out --wr 0x4810A010 1FD71E67

/usr/bin/mem_rdwr.out --wr 0x4810A014 304001C2

/usr/bin/mem_rdwr.out --wr 0x4810A018 FF200200

/usr/bin/mem_rdwr.out --wr 0x4810A01c 1B6C0B35

/usr/bin/mem_rdwr.out --wr 0x4810A020 1C0C0C30

/usr/bin/mem_rdwr.out --wr 0x4810A024 1C0C0C30

/usr/bin/mem_rdwr.out --wr 0x4810A028 00271360

/usr/bin/mem_rdwr.out --wr 0x4810A02c 3F150018

/usr/bin/mem_rdwr.out --wr 0x4810A030 3F2D0089

/usr/bin/mem_rdwr.out --wr 0x4810A034 00000139

/usr/bin/mem_rdwr.out --wr 0x4810A038 0003F32D

/usr/bin/mem_rdwr.out --wr 0x4810A03c 042D008A

/usr/bin/mem_rdwr.out --wr 0x4810A040 00019008

/usr/bin/mem_rdwr.out --wr 0x4810A044 01120151

/usr/bin/mem_rdwr.out --wr 0x4810A048 01001120

/usr/bin/mem_rdwr.out --wr 0x4810A04c 0100213A

/usr/bin/mem_rdwr.out --wr 0x4810A050 0013913B

/usr/bin/mem_rdwr.out --wr 0x4810A054 042D0082

/usr/bin/mem_rdwr.out --wr 0x4810A058 00019008

/usr/bin/mem_rdwr.out --wr 0x4810A05c 01120152

/usr/bin/mem_rdwr.out --wr 0x4810A060 01001120

/usr/bin/mem_rdwr.out --wr 0x4810A064 0100013A

/usr/bin/mem_rdwr.out --wr 0x4810A068 00000000

/usr/bin/mem_rdwr.out --wr 0x4810A06c 00000000

echo 0 > /sys/devices/platform/vpss/display1/enabled

echo 27000,1440/36/240/1,480/1/21/1,1 > /sys/devices/platform/vpss/display1/timings

echo doublediscrete,yuv422spuv,0/0/1/1 > /sys/devices/platform/vpss/display1/output

echo 1 > /sys/devices/platform/vpss/display1/enabled

/usr/bin/mem_rdwr.out --wr 0x4810A000 0x4420B05C // enable color bar