Other Parts Discussed in Thread: SYSBIOS

Tool/software: Starterware

Dear,

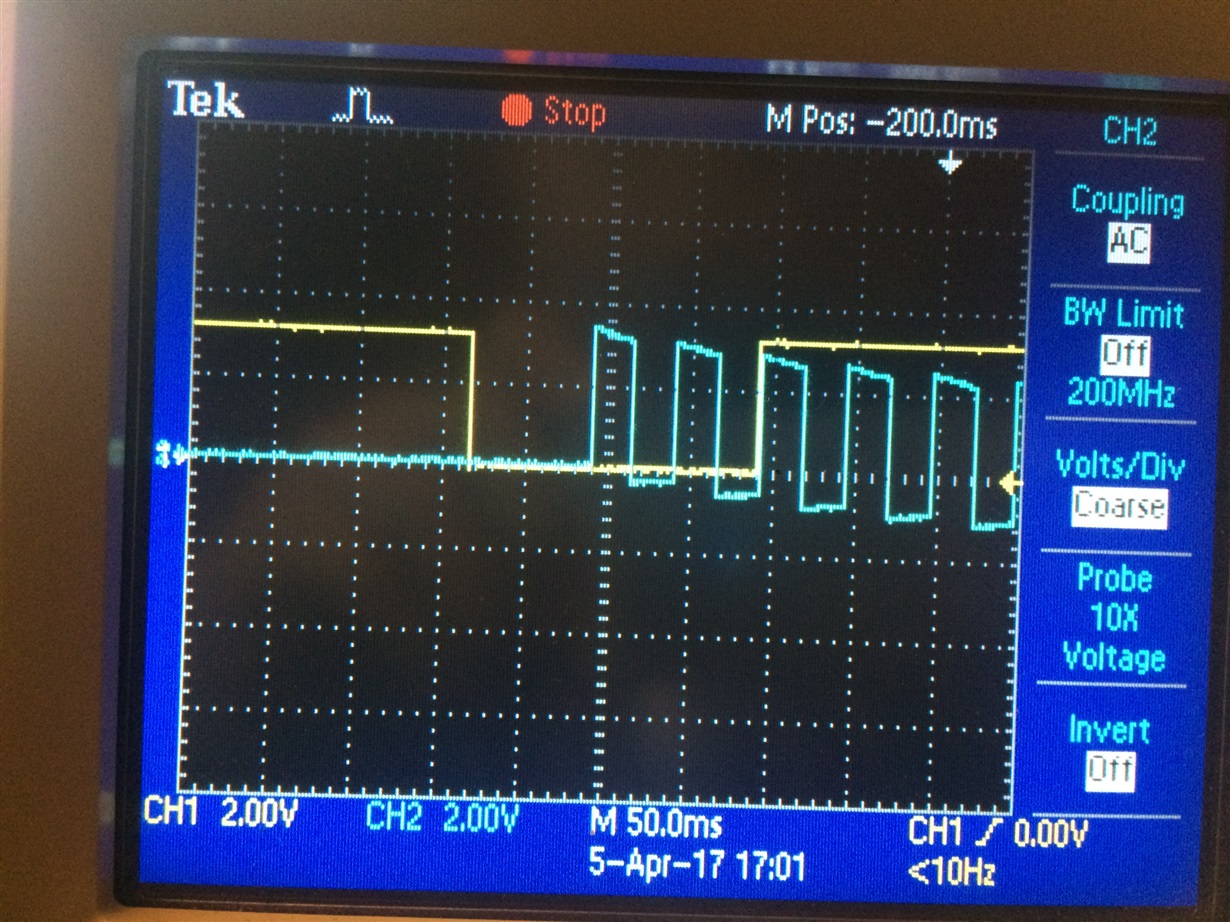

I put my device into DEEPSLEEP mode successfully. But then I can not recover the problem to work normally.

Could you please help me find out the mistakes?

Here is my code:

static void deep_sleep_mode (void)

{

// Step 1: Active Self-refresh mode to DDR2

// Clear self refresh/low power (SR_PD) bit to 0

HWREG(SOC_DDR2_0_CTRL_REGS + DDR2_MDDR_SDRCR) &= ~DDR2_MDDR_SDRCR_SR_PD;

// Set the low power mode enable

HWREG(SOC_DDR2_0_CTRL_REGS + DDR2_MDDR_SDRCR) |= DDR2_MDDR_SDRCR_LPMODEN;

// Step 2: Disable PHY SATA, USB2.0, USB1.1

// Step 3: put PLL/PLLC0 and PLL/PLLC1 in bypass mode

/*PLLEN = 0 put pll in bypass mode in PLL0 */

HWREG(SOC_PLLC_0_REGS + PLLC_PLLCTL) &= ~PLLC_PLLCTL_PLLEN;

/*PLLEN = 0 put pll in bypass mode in PLL1 */

HWREG(SOC_PLLC_1_REGS + PLLC_PLLCTL) &= ~PLLC_PLLCTL_PLLEN;

// Step 4: Power down PLL 0 and PLL 1

/*PLLPWRDN = 1 in PLL0 */

HWREG(SOC_PLLC_0_REGS + PLLC_PLLCTL) |= PLLC_PLLCTL_PLLPWRDN;

/*PLLPWRDN = 1 in PLL1 */

HWREG(SOC_PLLC_1_REGS + PLLC_PLLCTL) |= PLLC_PLLCTL_PLLPWRDN;

// Step 5: Config DEEPSLEEP pin as Input only

// Config GP0[8] - DEEPSLEEP pin - pin number 9

uint32_t savePinmux = (HWREG(SOC_SYSCFG_0_REGS + SYSCFG0_PINMUX(0)) &

~(SYSCFG_PINMUX0_PINMUX0_31_28));

HWREG(SOC_SYSCFG_0_REGS + SYSCFG0_PINMUX(0)) =

(PINMUX0_GPIO0_8_ENABLE | savePinmux);

// Config this pin as input-only

GPIODirModeSet(SOC_GPIO_0_REGS, 9, GPIO_DIR_INPUT);

// Step 6: Config delay in the SLEEPCOUNT bit (ex: 0x0F)

HWREG(SOC_SYSCFG_1_REGS + SYSCFG1_DEEPSLEEP) |= (0x0F & SYSCFG1_DEEPSLEEP_SLEEPCOUNT);

// Step 7: set SLEEPENABLE bit in DEEPSLEEP to 1

HWREG(SOC_SYSCFG_1_REGS + SYSCFG1_DEEPSLEEP) |= SYSCFG1_DEEPSLEEP_SLEEPENABLE;

// Step 8: polling bit SLEEPCOMPLETE

while (~(SYSCFG1_DEEPSLEEP_SLEEPCOMPLETE &

HWREG(SOC_SYSCFG_1_REGS + SYSCFG1_DEEPSLEEP)))

{

}

// Step 9: Drive the DEEPSLEEP pin low

/***************************EXIT DEEPSLEEP MODE*****************************/

// Step 10: clear SLEEPENABLE bit in DEEPSLEEP to 0

HWREG(SOC_SYSCFG_1_REGS + SYSCFG1_DEEPSLEEP) &= ~SYSCFG1_DEEPSLEEP_SLEEPENABLE;

// Step 11: initialize PLL again

/* Clear PLLRST bit in PLLCTL to 0 */

HWREG(SOC_PLLC_0_REGS + PLLC_PLLCTL) &= ~PLLC_PLLCTL_PLLRST;

HWREG(SOC_PLLC_1_REGS + PLLC_PLLCTL) &= ~PLLC_PLLCTL_PLLRST;

/* Clear PLLPWRDN bit in PLLCTL*/

HWREG(SOC_PLLC_0_REGS + PLLC_PLLCTL) &= ~PLLC_PLLCTL_PLLPWRDN;

HWREG(SOC_PLLC_1_REGS + PLLC_PLLCTL) &= ~PLLC_PLLCTL_PLLPWRDN;

/* Set PLLRST bit in PLLCTL to 1 - out of reset*/

HWREG(SOC_PLLC_0_REGS + PLLC_PLLCTL) |= PLLC_PLLCTL_PLLRST;

HWREG(SOC_PLLC_1_REGS + PLLC_PLLCTL) |= PLLC_PLLCTL_PLLRST;

/* Wait for PLL to lock*/

/* Wait for 300 counts*/

Delay (300);

/*Set the PLLEN bit in PLLCTL to 1 - remove bypass mode*/

HWREG(SOC_PLLC_0_REGS + PLLC_PLLCTL) |= PLLC_PLLCTL_PLLEN;

HWREG(SOC_PLLC_1_REGS + PLLC_PLLCTL) |= PLLC_PLLCTL_PLLEN;

// Step 12: Enable clock DDR

/* Enable clock to SDRAM */

PSCModuleControl(SOC_PSC_1_REGS, HW_PSC_DDR2_MDDR, 0,PSC_MDCTL_NEXT_ENABLE);

/* Set RESET_PHY bit in DDR PHY*/

HWREG(SOC_DDR2_0_CTRL_REGS + DDR2_MDR_DRPYCRC) = DDR2_MDDR_DRPYRCR_RESET_PHY;

/* Clear MCLKSTOPEN bit in SDRCR*/

HWREG(SOC_DDR2_0_CTRL_REGS + DDR2_MDDR_SDRCR) &= ~DDR2_MDDR_SDRCR_MCLKSTOPEN;

/* Disable Self refresh rate */

// clear the low power mode

HWREG(SOC_DDR2_0_CTRL_REGS + DDR2_MDDR_SDRCR) &= ~DDR2_MDDR_SDRCR_LPMODEN;

}

Regards, Nghia Quy