Hello.

I have a great problem with PCM4220 audio codec.

My configuration:

1) PCM4220

- Master mode

- Double Speed mode

- Classic filter response

- SUB0 = 0 and SUB1 = 0: Sub-frame 0

- OWL0 = 0 and OWL1 = 0: 24-bits

- FMT0 = 1 and FMT1 = 0: I2S

Audio serial port bit clock - 6,14407 MHz

Audio serial port left/right word clock - 96 KHz

Master clock - 12,2881 MHz

2) DSP (TMS320 C6745)

Codec connected through McASP.

Master clock - 24,576 MHz

Voltages on PCM4220:

VINR- (1,7354V)

VINR+ (2,1754V)

VINL- (1,7354V)

VINL+ (2,1754V)

My Problem: I have incorrect data from audio codec.

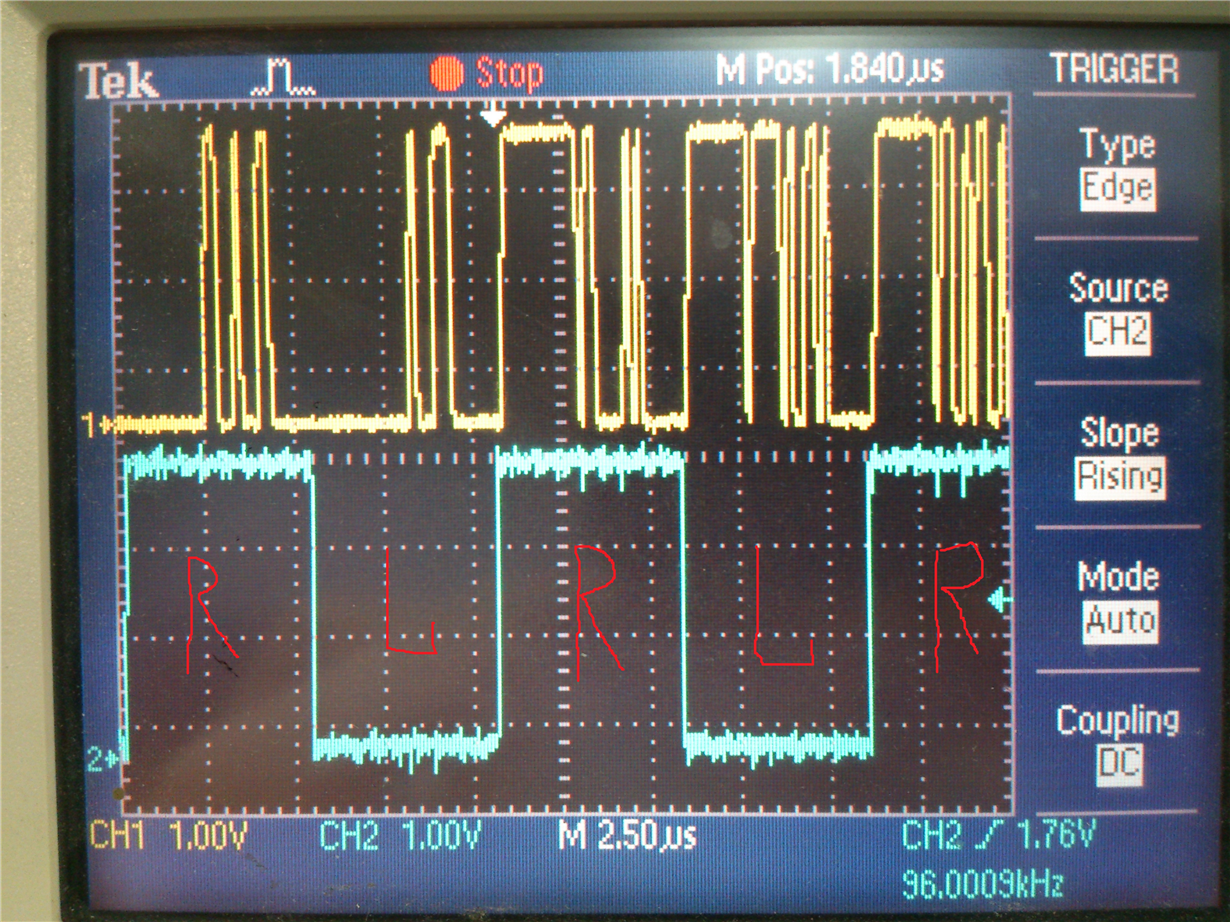

CH1 - DATA Pin

CH2 - LRCK Pin

Why data from left and right channel are very different ?

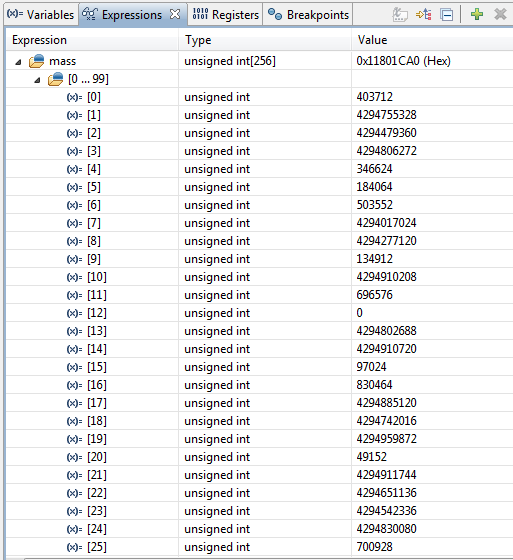

This is confirmed by data from buffer.

This problem hurts me a one week. I've tried the different chip (PCM4220), check my schematic with datasheet, but I don't have any result. Where is my mistake ?

Thanks.