Part Number: DP83TG720S-Q1

Hi TI,

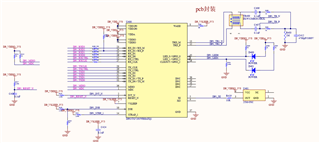

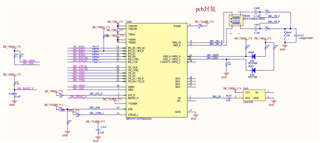

On board we have DP83TG720S-Q1 integrated,and we are using fpga to drive 1000Base-T1 interface.

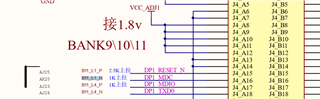

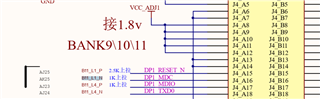

By default, MDI Slave mode is configured by using external pullup 1K resistor on LED_0 pin.I want to configure as slave-mode in normal mode.

I tried just manually to set register 0x834 with 0x8001 value,but it remains the "master" all the time.

To configure slave mode,does any other register need to set?If need to configure other registers,I want to know the minimum register configuration.