Other Parts Discussed in Thread: AM3352

Hi experts,

I have a boards designed with 2 DP83867CRRGZ Gigabit PHY, and they are all connected with TI AM3352.

- One is connected with a 100M net work, it always worked well;

- The other one is connected with Gigabit network, it will work well like 5 hours, 10 hours, or even 20 hours, but some how it will stop working. I measured two boards:

For #1,

- When network is down, RJ45 link LED is on and activity LED is off

- 1.0V, 2.5V, 3.3V and Bias (1V) are all stable

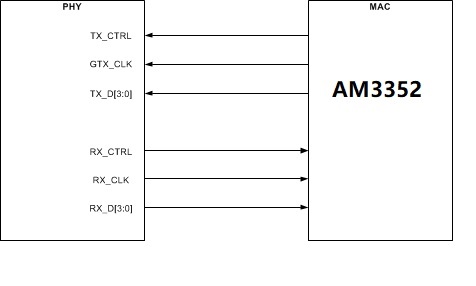

- RXCLK is always low, output of PHY and input of proc.

- RXCTRL is always low.

- GTXCLK is 25MHz, this is driven from MAC to PHY.

- TXCTRL is a 6us pulse every about 1 second.

- CLKOUT of test point is a stable 25MHz.

For #2 board

- When network is down, both RJ45 Link LED is on and RJ45 ACT led is blinking.

- 2.5V, 1.0V, 3.3V and Bias are all clean.

- RXCLK is 125MHz, from PHY to MAC

- RXCTL is 1us width pulse, every less than 1 second

- TXCLK is 25Mhz, MAC to PHY.

- TXCTL is always low,

- CLKOUT is a stable 25MHz.

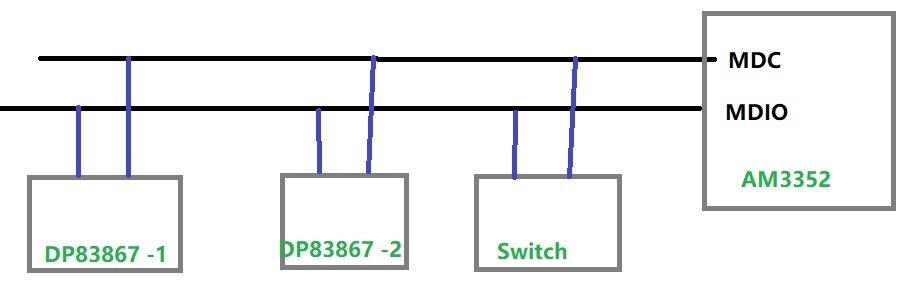

Meanwhile in Linux of AM3352, MDC/MDIO bus can't detect this phy, all the registers read back from these 2 boards are "FF", while the other two devices in the same MDC/MDIO bus are working well.

Any suggestion?

Thanks

Chris