Hi Could you please help to answer my question, thank you very much!

Q1: The software version is α version or β version? some register is only β version active in DS depiction

Q2:if need configure the CTLE Boost value/EQ Gain/VGA Gain register at GBE datarate, what is impact with different value? how to configure these register

Q3: what situation is 0x40~0x53 uesed in ? if set to adapt mode 0 , the register is active still?

Q4: What is the function of CTLE bypass? if under bypass mode , is FIR moden not active ?

Q5: the FIR after Driver is also active when use at bypass mode . if active ,wich regiseter need configure?

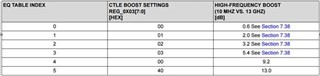

our situation is used at GBE datarate , when test the Serder self loop BER testing , the BER is large. if configre the 0x41~0x53 register used following setting , the test is ok ( no bit error with 24HRs)

Is the following configuratio correct?

that'all

thanks

Ekin