Hi TI,

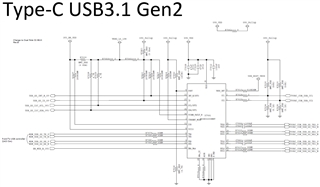

I have a project using HD3SS3220 for type C port (DRP mode), and I have a questions Below,

1. Is SS+ (Gen2 10Gbps) data transfer using all inter-pair channels(SS1&SS2) at same time?

(ex. USB controller~MUX: 10Gbps per SS channel,

After deMUX switching & in Type-C USB cable : 5Gbps per SS1&SS2 channel (inter-pair)

After MUX switching in the attached device : 10Gbps per SS channel )

Or is it 10Gbps data transfer between Host deMUX and Device MUX with one fixed channel(SS1 or SS2)?

2. Is length matching between SS Tx and SS Rx necessary? Your document says it's not necessary, so I'll ask you to confirm. (SLLA414.pdf 6page)

3. Is length matching between SS channels(Inter-Pair Skew) necessary? Your document says it's not necessary, so I'll ask you to confirm. (SLLA414.pdf 6page)

4. Can I connect the circuit by swapping P and N for SS Intra-pair signal trace optimization? Your document says it's possible, so I'll ask you to confirm. (HD3SS3220 datasheet 26page)

5. Is it okay to trace the SS line with a thickness of 0.2mm on the outer PCB layer to minimize the Surface-Mount Device Pad Discontinuity caused by the AC coupling capacitor (0603 size)? 85ohm impedance matching will be matched by inner layer fillcut.

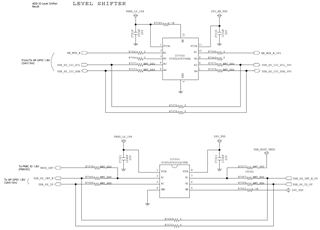

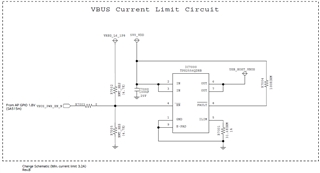

I attach my schematics, please help to review if the design has other issues, thanks.