Part Number: DS90UB953-Q1

Hi Team,

One of our customers has the following questions:

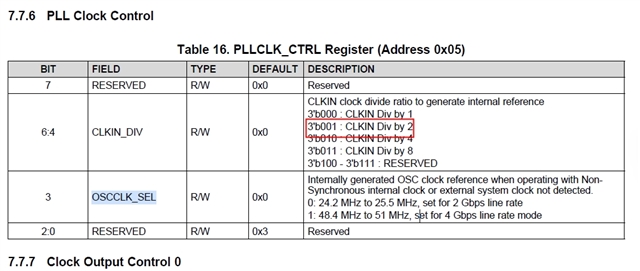

DS90UB953 is used as video output product, and 964 is used together without POC. The two SerDes are powered separately. Synchronous mode is used. CLK of 953 is provided through FPD-Link of 964.

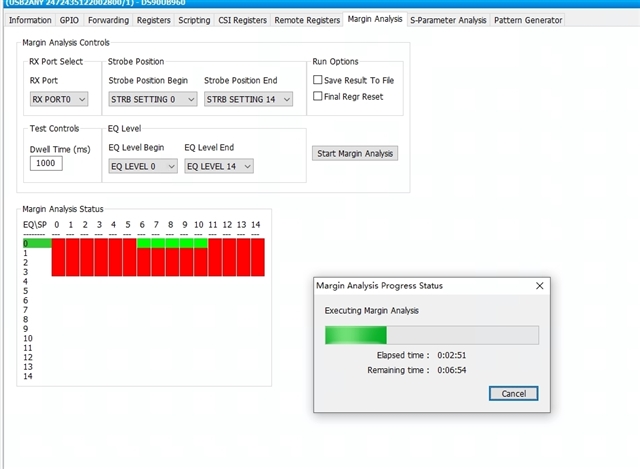

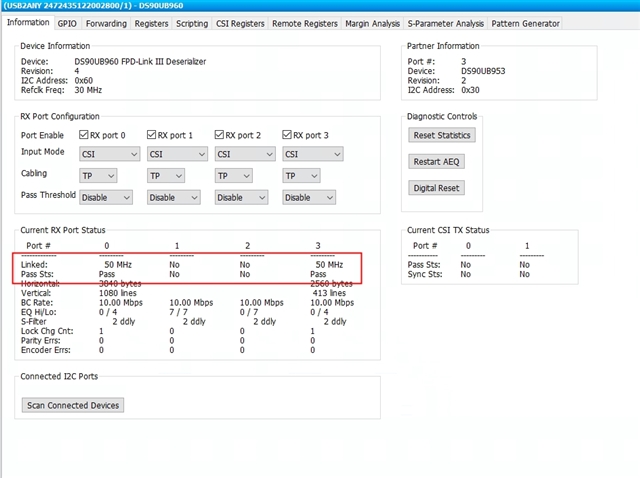

During the low temperature (- 40) experiment, the video output is abnormal and the Link cannot be connected. Using TI's 964 demo to test FPD-Link, it is found that the Link cannot be connected at low temperature (- 40 ℃), and the link state is unstable, changing between disconnected and connected states.

At this time, the power supply of 953 is stable. Return to normal temperature and work normally. The harness and other cameras are the same set of harness, and other cameras are normal at low temperature. I don't know what may be wrong with this situation.

Best Regards,

Amy Luo