Hi Team,

Our customer design uses the TCA6424A. Due to delivery problems, they decided to use TCA6424 as an alternative based on the Errata of the datasheet.

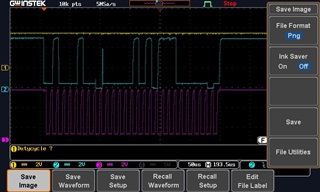

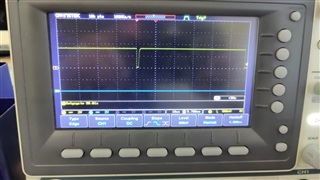

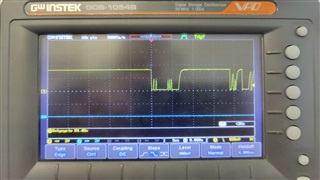

However, they observed that the interrupt does not behave as with the previous chip. It instantly ge de-asserted (see attached picture).

- Reading from register 00h is never our last command. We always read register 00h, 01h and 02h after each other in this order.

- We have no other I2C slave connected (only the STM32 as master)

The interrupt is only very shortly active around 1us and gets immediately de-asserted. That you see several activations of it comes from a bouncing switch as they have an RC filter on the electronic (interrupt line) these short pulses gets filtered.

According to the customer, The behavior which they observe is not related to the Errata and they suspect that the chip has more differences to the TCA6424A than listed in the Errata.

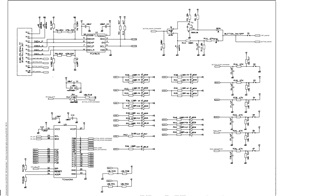

Here is the schematic for additional information:

The TCA6424 replaces U3 on the HMI (separate PCB) and is connected by wire to the Baseboard. On the baseboard is a STM32 (the other side of the I2C). For better signal quality over wire, they implemented PCA9615 on both sides.

Can you help the customer to handle the chip same the same as the TCA6424A?

Regards,

Marvin