Other Parts Discussed in Thread: LMK04828,

Hi Team,

I have some questions about retimer. Could you please help me on that?

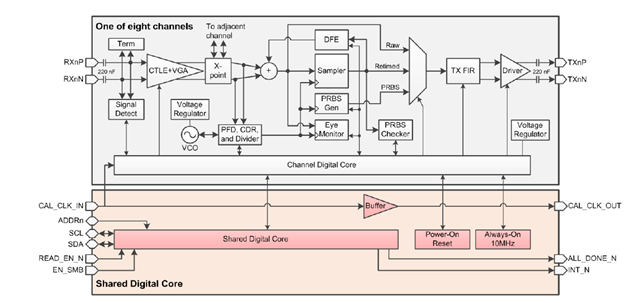

1. I have two SFP28 SIP optical ports on the boards and the trace between SIP and ASIC are difference between them, one is much longer than another and I need to use 25G retimer to compensate the IL. I am concern about the lane delay introduced by the retimer will make two SIP to ASIC lane delay different during multiple start up. Because I suppose that the CTLE and DFE adaption time is random, am I right? If yes, how could we manager this issue?

2. Does the CDR in the retimer is simlar as a PLL? The input is the raw data and the output is the pure clock which from integrate VCO. If the error between input data frequency and output frequency with a configurable certain range and exceed the PPM counter threshold, the CDR will lock.

3. If it is yes, why we add an external clock to run the PPM counter? I saw other TI device such as LMK04828 it didn't have the requirement for an external oscillator.

4. How to choose a FIR filter main, pre, post cursor value when given eye height and channel IL loss? I look through the DS250DF230 datasheet, how to interpret this figure with the FIR table?

Thanks.

B.R.

Zhizhao