Hi

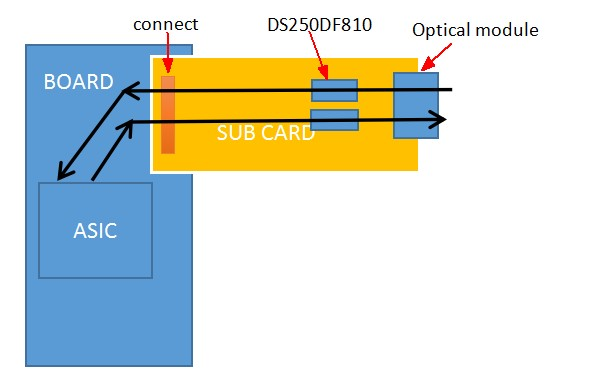

interface is 100G,To eliminate the retimer Rx over-equalization problem,

1、We change the RX output emphasis control register in the optical module from 3dB to 0dB;

2、Forcing CTLE = 0x00 combined with limiting mode and reduced CTLE bias current

reg value mask

13 0x04 0x24

1a 0x00 0x08

2d 0x08 0x08

03 0x01 0xff

Rx adapt Mode set adapt-mode = 2;

Front-port ingress in 《DS250DF810_SNLU182_Programmers_Guide_confidential.pdf》 used for configuration reference;

When our equipment is connected with the customer's equipment, some modules are in use, and our receiving port is normal without wrong packets, but some modules are in use, and there are wrong packets that cannot be eliminated。The module is normally connected between other devices without wrong package.The wiring length from optical module to retimer Rx is between 0.8-4.2 inches,The board material is M6G;

It still feels like an over equalization problem!

Is there any other solution?

Is there any method to determine the adaptation parameters of retimer in our application scenario?

Thanks