Hello:

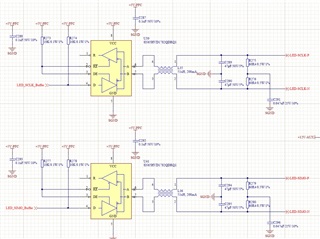

The customer is currently using a TI chip SN65HVD1782QDRQ1, which fails after power on. They use two chips to convert clock signal CLK and data signal SIMO of SPI signal into differential signal output. The schematic diagram is shown below. In the past year, there were 3 or 4 random failures of the chip after power on, all of which were U39 failures, which showed that the chip output level was constant.

Please ask if you have encountered similar problems, or help confirm whether there are defects in the schematic design? thank you very much!

A and B are the same

A and B are the same