We've used the TL28L92 to replace an obsolete NXP SC28L92 and found it works fine in 8-bit mode but does work in Multi-drop (9-bit) mode.

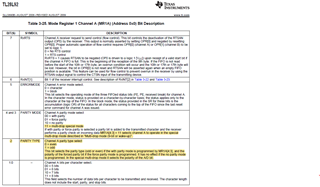

In Muti-drop (9-bit) mode the PARITY TYPE bit in Mode Register 1 determines the state of the 9th bit, the A/D bit, when a byte is transmitted. The state of the PARITY TYPE bit is supposed to be captured when a byte is written to the TX FIFO so that each byte is eventually transmitted with the previously captured 9th bit. It appears that the TL28L92 is not capturing the PARITY TYPE state and is instead using the current state of the PARITY TYPE bit while transmitting each byte.