Other Parts Discussed in Thread: TDES954, , TSER953

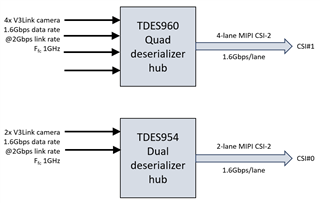

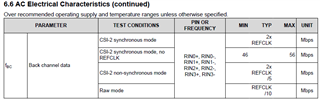

I'm designing a surround view system based on TSER953 serializers in camera board and TDES960 and TDES954 deserializers in processor board for up to six cameras through two MIPI CSI-2 input ports. The cameras will be full HD 1920x1080 pixels at 30Hz frame rate (1080p30). This means roughly 1.5Gbps data rate, when MIPI CSI-2 overhead is not considered. In another thread it was discussed that 2Gbps link rate will be good for 1.6Gbps. For host CSI-2 port I would then use 4-lanes with 1.6Gbps per lane for TDES960 and 2-lanes for TDES954.

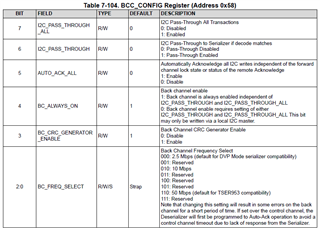

I have been reading through the TDES960 datasheet and I would need some clarification. I was planning to use synchronous mode, in which V3Link forward channel rate is a fixed value of 160 × REFCLK. In table 7-2 REFCLK oscillator specifications the frequency is min 23MHz, max 26MHz, which would mean V2Link forward channel rate of 3.68-4.16Gbps. Does this mean that 2Gbps link rate can't be used in synchronous mode? If TSER953 is used in non-synchronous mode, V3Link line rate is typically CLK_IN × 80, which would mean 2Gbps link rate with 25MHz oscillator for serializer.

However, in device status register (DEVICE_STS) bit 4 REFCLK_VALID is set when "REFCLK frequency between 12 MHz and 64 MHz". This would indicate that I could use for example 12.5MHz oscillator and get 2Gbps (160 x 12.5MHz) link rate in synchronous mode.

Which is the correct way to implement 4x 1.6Gbps V3Link cameras deserialized to 4-lane CSI-2 port with 1.6Gbps per lane?