Other Parts Discussed in Thread: TUSB8044

Dear team,

1. At datasheet, I2C speed is 100K and 400K(default) and then, How about SMBus speed? Is it same with I2C speed?

Please let me know maximum speed of SMBus interface.

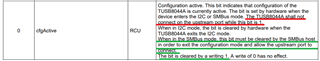

2. After changing internal register of TUSB8044A using SMBus, In order to re-configuration, Does the customer have to set smbusRst bit to 1 only or Is GRSTz reset needed?

Thank you.