Hi expert,

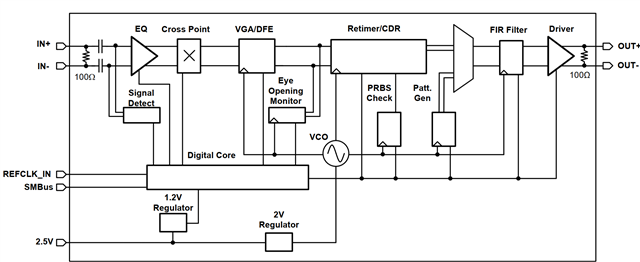

In my design, DS125DF1610 is being used in the middle of data path, e.g., A----DS125DF1610------B, running at 10Gbps

I was able to control the outputs A, so it can drive electrical idle waveform(both P and N to the same common mode voltage),

When my projects are running, the outputs of A will be like Electrical idle, then normal data, then Electrical idle, then normal data, etc, the EI time is more than 100ms?

I ran this test for 490 times, since the 491th cycle I got an error.

1) When A is driving EI, Signal Detect will be invalid, 0x78 will be 0x00

2) When A is driving normal data, Signal Detect will be valid, but 0x78 is 0x20, CDR is unlock,

3) I tried to control 0xa to 0xc to reset this channel, still the same phenomenon.

4) I used the hardware reset pin to reset the whole chip, 16lane, then my test is working again.

Is this a bug? Anything wrong with my flow?

Thanks

Chris