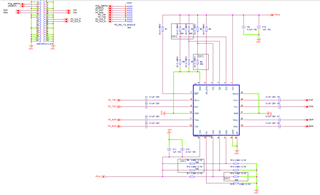

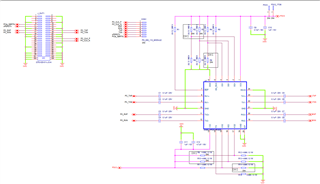

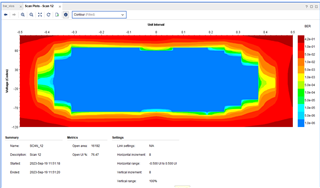

We use the redriver chip SN65LVPE501 in the PCIE link. Currently, there is a phenomenon that cannot be identified. Do you have any recommended reference design?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.