Hi

When my customer tested the topology of BMC (Master)-PCA9306-slaves.

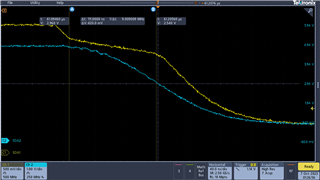

They found that there was an obvious groove on the falling edge of SDA in the read direction sent by different slaves measured at PCA9306, with the following two phenomena,

As shown in Figure 1 (1.157V~1.216V), Figure 2 (0.485V~0.549V).

Testing the read signal on the BMC side did not find this problem; please help confirm whether this problem is risky?