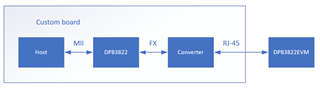

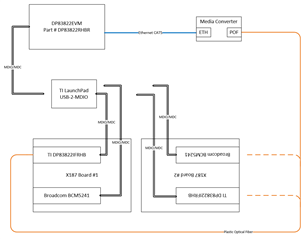

Other Parts Discussed in Thread: DP83822EVM, USB-2-MDIO

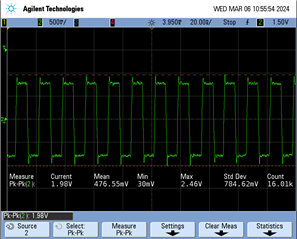

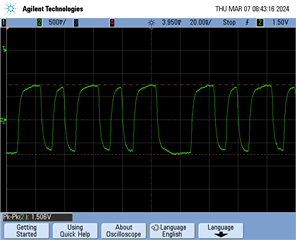

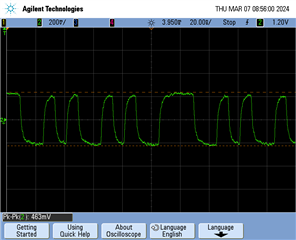

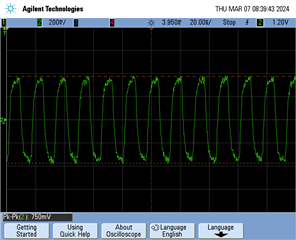

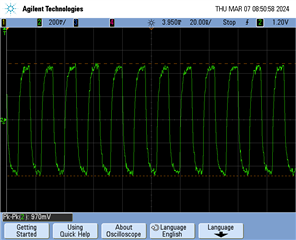

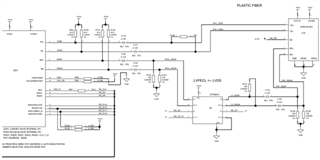

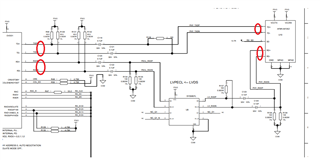

I've got the TI PHY and Broadcom PHY both configured for fiber, disable A/N, 100Mbps, full-duplex.

They are connected to each other transmitting dummy data and I expected this would be successful right out of the box.

For reference, connecting two TI PHYs together in the same fashion was successful.

As I understand, these are both transmitting 4B5B codes and the data is NRZI.

What could be the incompatibility?