Other Parts Discussed in Thread: DS25CP104A

Hello, we are going to create a design based on the DS25BR400TSQ and FPGA, but we do not fully understand the compatibility of the interfaces, in particular:

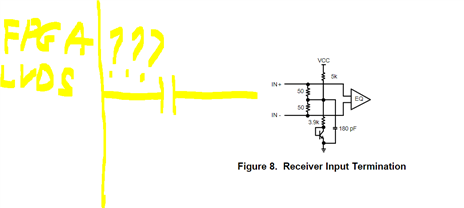

1) Is it necessary to put separate capacitors on the input of the DS25BR400TSQ microcircuit, since it has a signal displacement circuit and the LVDS signal will be supplied?

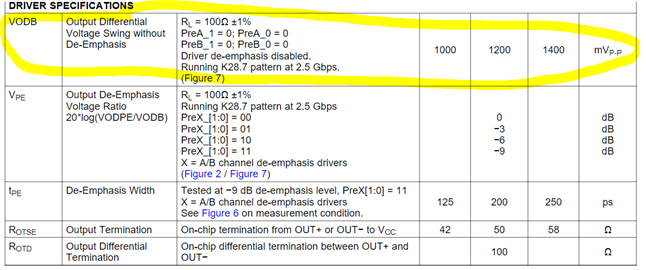

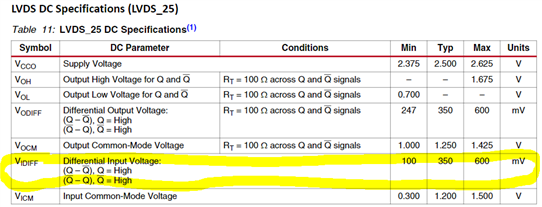

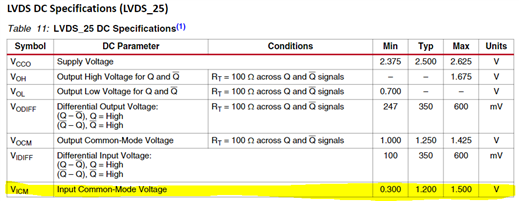

2) In the first scheme, we will connect this microcircuit to the Artix7 FPGA, and in the second to the Arria10. The question is that the VODB parameter in the DS25BR400 is too high, namely it can be from 1 to 1.4V, when the maximum Vidiff can be 0.6V on the Artix7, is this critical?

DS25BR400:

Artix7 FPGA:

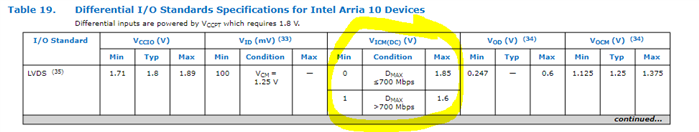

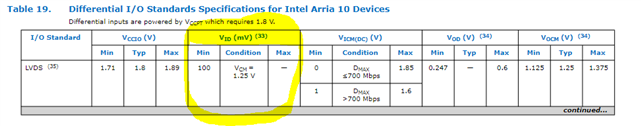

Arria10 FPGA:

3) What to do with the high value of Common mode 2.7 V that the DS25BR400 microcircuit produces? because the maximum value of this parameter in Artix7 reaches 1.5 V

DS25BR400:

Artix7 FPGA:

Arria10 FPGA: