Hello,

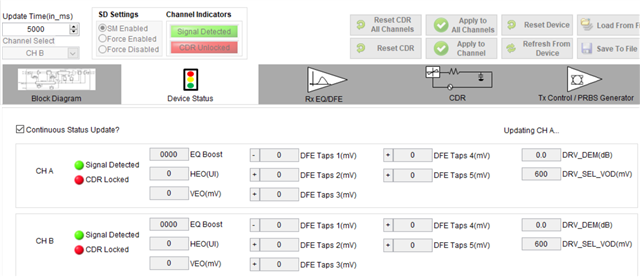

I have a custom a PCB design that involves the DS110DF111 to interface between a processor to Cisco optical switch. I'm currently testing with Cisco Compatible Duplex 10GBASE-ZR/ZW Ethernet 10G Ethernet / 8G FC SFP+ transceivers designed for long distance optical communications up to 80 km with signaling rates up to 10.3125 Gbps, which are connected via optical patch cables between custom PCB SFP+ ports to the SFP+ ports on the switch. Currently, the CDR is not locked on both CHA and CHB and no link is established. I would like to know if the DS110DF111 supports 10GBASE-ZR and what other retimer settings I could try to help establish a link. Please see attached device status screenshots from the SigCon Architect GUI and the register .cfg file if this helps. Also attached is a snippet of the schematic for the PCB design using the retimer. Thank you in advance for any help that can be provided!