Tool/software:

HI,Team.

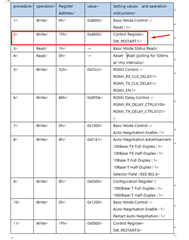

We plan to use DP83867IR for product function design, using RGMII mode.

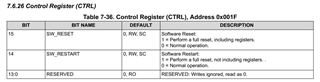

I found the register mapping table in the manual. It is not clear how to use these registers. Can TI provide the initialization software flow chart of DP83867IR, the software flow chart of sending/receiving. It is best to be able to operate with registers. Thank you.