Part Number: DP83869HM

Other Parts Discussed in Thread: DP83869

Tool/software:

Dear team,

There is issue on customer board. The customer use DP83869 device on both board.

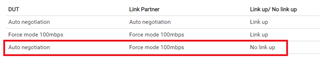

First board power on, DP83869 is Forced 100M mode, but we can see abnormal voltage other side board(second board). Although we don't supply any power at second board but we can see about 400mV voltage on VDDA2P5 line and 50mV on VDDIO line. Is this phenomenon normal situation? Please let me know your opinion.

It is critical issue. please let me know your opinion as soon as possible.

Thank you.