Tool/software:

Hi,

We are having difficulty achieving CDR lock in the following condition

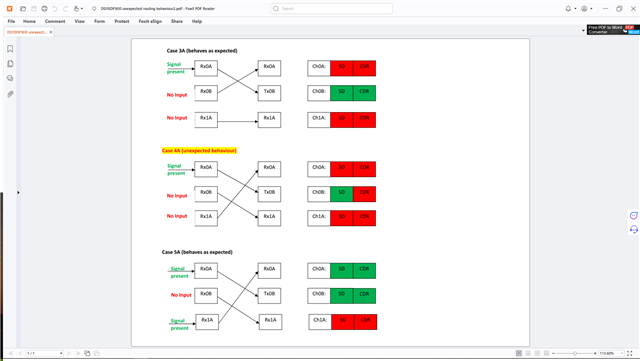

We are using the SigCon Architect tool to configure the device and we have a signal input into RX0B

When we have TX0B looking at RX0B we achieve a CDR lock

If we configure TX1A to then look at RX0B we achieve CDR lock on both RX0B and TX1A which makes sense (apart from having not configured master/slave bits)

However if we then configure TX0B to look at an input without a signal and keep TX 1A looking at RX0B (which we know is present) we loose both the SD and CDR for TX0B but also loose the CDR on TX1A?.

If we then configure TX0B to look at RX0B again, we get CDR lock on both TX0B and TX1A,

Can you tell me the correct way to reroute a one to one configuration so that you can achieve a CDR lock when your output channel is not the same as the input channel?

Thanks,

Dave