Other Parts Discussed in Thread: DS560DF810, TINA-TI

Tool/software:

Hi,

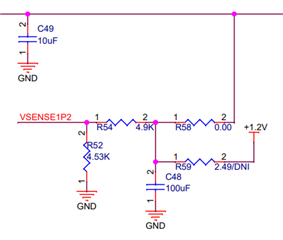

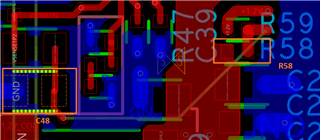

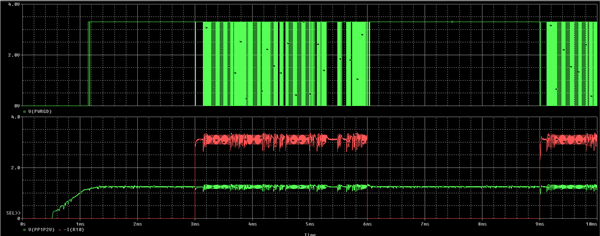

I have a board with TPS54678 that powers a DS560DF810. Whenever I perform a soft reset on the DS560DF810 device, I observe the output of the TPS54678 starts oscillating and the power good pin state toggles. A soft reset of the DS560DF810 results in a load step where current decrease from ~2.5A to ~0.5A, so roughly a -2A step.

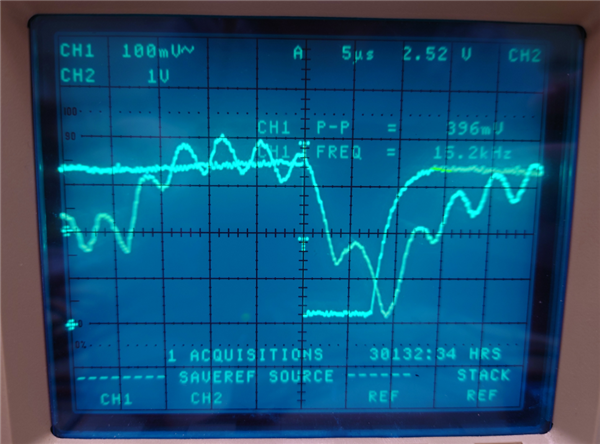

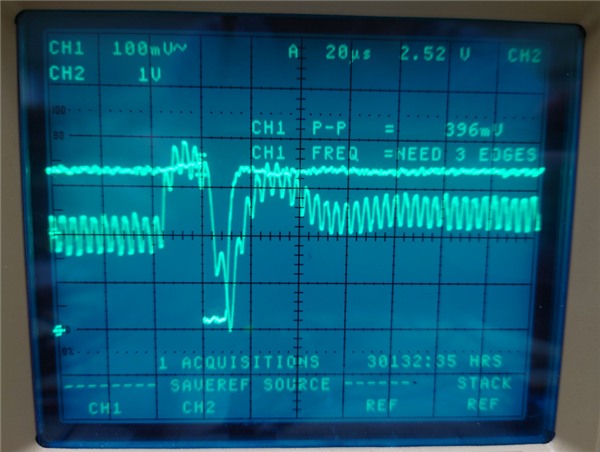

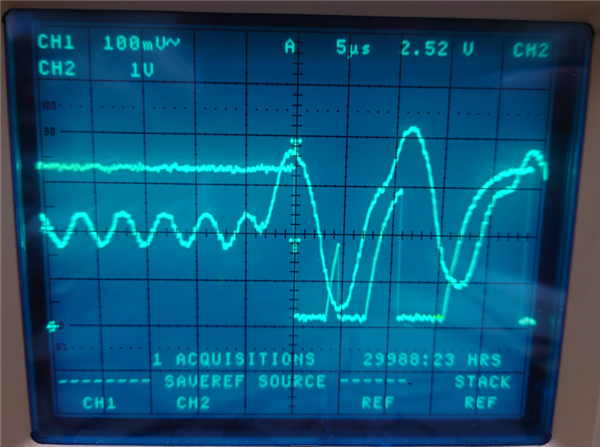

I'm not sure if the magnitude of the ripple shown in these scope captures is accurate, did not probe with tip/barrel method. However, I think this shows power good output correlates to exceeding Vout thresholds.

Initial transient resulting in this behavior:

- CH1: Vout, AC coupled

- CH2: Power good, DC coupled

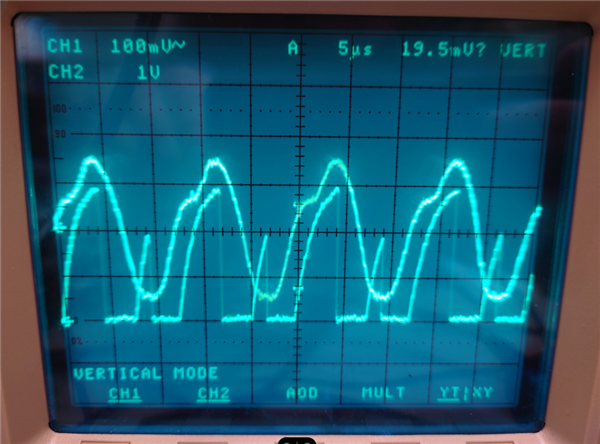

"Steady state" behavior of Vout after load step:

- CH1: Vout, AC coupled

- CH2: Power good, DC coupled

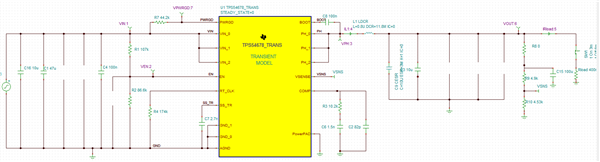

Can you help advise on how this can be resolved? Is this something that could be due to the compensation network or a lack of Cout?

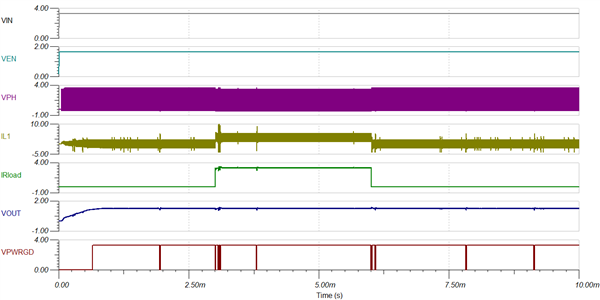

I've also worked on simulating this, but I'm seeing conflicting simulation results between tina-ti and pspice when it comes to the power good state and how load steps are handled. Please let me know if you have any thoughts on the simulation discrepancy. Neither simulation shows this "oscillation" behavior observed on the board.

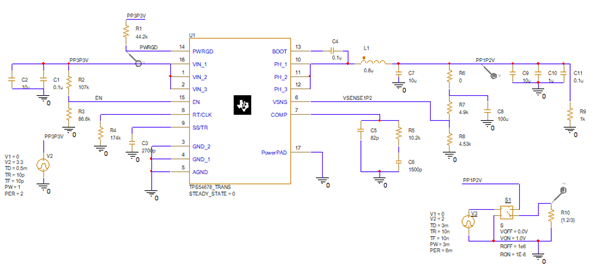

Tina-TI

Pspice

Thanks,

Drew