Tool/software:

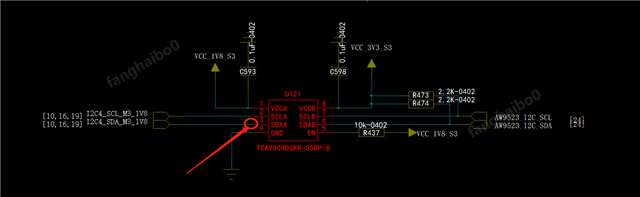

As shown in the figure, the chip uses TCA9509DGKR internal A end I2C has a pull-up, B end no pull (need external up) to achieve 1.8V to 3.3V I2C level conversion. After I2C mounted the device, it was found that the SDA waveform at the A end was abnormal, and the semi-high level state appeared, and the 0 state could not be pulled down, and could only reach 0.43V. The SDA of the B terminal is normal. Therefore, many cross implementations were made, such as replacing the matching of the AB end resistance (from 1.5-2.2-3.3-4.7-5.1-10K) and removing the external resistance of the A end were ineffective, and the SDA was still not low. The level conversion built manually by MOS can pull down the SDA, and the final judgment is caused by the I2C level chip, but I do not know the specific reason.