Tool/software:

Hi Team,

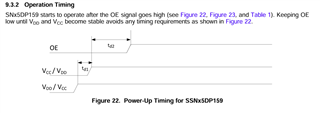

1. If i give enough time for OE to be de-asserted until which all the VCC and VDD are stable, is there still a requirement of 'td1' to be taken into consideration since there will be a delay of 1.4ms between VCC and VDD in my design?

2. What is maximum acceptable time for OE to be kept de-asserted? ( I am using RC filter for delay)

3. Also, is the delay of 1.4ms between them acceptable?

4. Also can the stability of VCC before VDD or vice versa can be ignored?

Image attached below:

Thanks,

M Karthik