Tool/software:

Hello,

my name is Roberto Teodori and I need a clarification about one of the features listed in the TMDS171/I Datasheet.

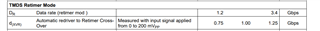

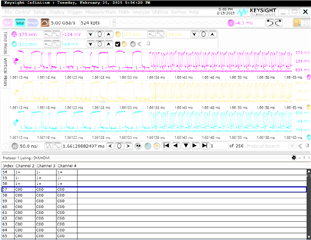

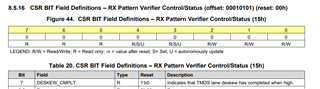

I' m referring to Inter-Pair Skew Compensation of 5+ Bits.

5+ Bits means that skew compensation works for more than 5 Bits, for example can compensate up to 10 bits?

Thank you for your support

Best Regards

Roberto Teodori