Tool/software:

Dear.

We are currently developing a system using deserializer(DS90UB954-Q1)

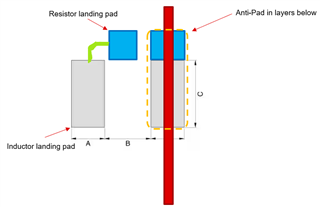

POC filter designing by selecting TDK network8.

The application requires L2 and R2 to be connected to the RIN+ line simultaneously.

I would like to inquire about the routing guide accordingly.