Other Parts Discussed in Thread: SN75LVPE5421

Tool/software:

Hello, Ti support team

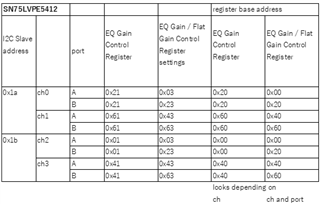

I am conducting experiments using the ICs SN75LVPE5412 and SN75LVPE5421, changing the EQ Gain and Flat Gain settings.

Could you please tell me the register addresses used when configuring these two settings via I2C communication?

Table 6-5 in the datasheet includes the following information.

Could you explain the differences between addresses 0x00 and 0x20, and between 0x40 and 0x60?

When testing with the actual hardware, it seems that the addresses are used differently depending on whether port A or B is selected, but I couldn't find any mention of this in the datasheet.

If there is any detailed documentation about the Register Base Address, could you please share it with me?

Table 6-5

Channel Registers Base Address

Channel Bank 0 Access Channel Bank 1 Access

0x00 Channel 0 registers Channel 2 registers

0x20 Channel 0 registers Channel 2 registers

0x40 Channel 1 registers Channel 3 registers

0x60 Channel 1 registers Channel 3 registers