Tool/software:

Hi

I'm using a PHY [DP83867IRRGZT] on a board I designed, but during shutdown sequence checks it is behaving differently than expected, violating the FPGA shutdown sequence, so I'm looking for a way to improve this.

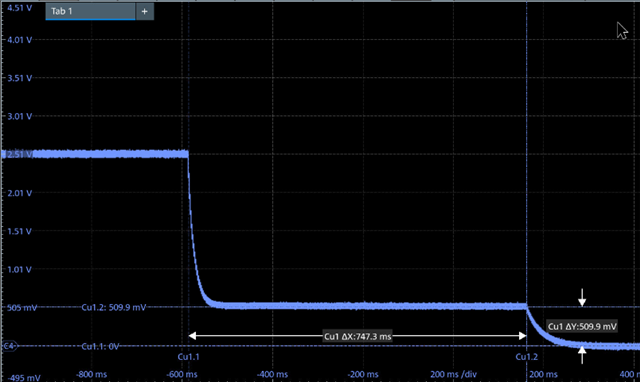

After powering on the system and establishing Ethernet communication, when powering off the system, the 2.5V voltage supplied to the PHY remains at 500mV for approximately 750ms, then discharges to 0mV over 100ms.

If Ethernet communication is not established, the voltage does not remain at 500mV, and immediately discharges to 0mV.

The PHY is operating with a dual power supply configuration (1.0V, 2.5V) and the VDDIO-Supply supplies 1.8V.

The MODE design is as follows:

RX_D0: PHY_ADD0,1 ⇒ MODE1

RX_D1: PHY_ADD2,3 ⇒ MODE1

RX_CTRL: Autoneg ⇒ MODE3

LED_2: RGMII Clock Skew Tx[0],[1] ⇒ MODE1

LED_1: ANEG_SEL, RGMII Clock Skew Tx[2] ⇒ MODE1

LED_0: MirrorEnable ⇒ MODE1

GPIO_0: RGMII Clock Skew[0] ⇒ MODE1

GPIO_1: RGMII Clock Skew[1,2] ⇒ MODE1

I will post the captured waveform.

Is this a characteristic of the PHY?

Or can it be resolved by adjusting the OHY settings?

Please let me know.

Best Regard,Kato