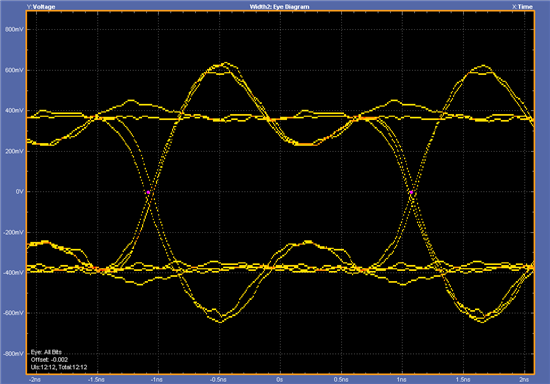

I was able to attain an Eye diagram from pins 38 and 39 of Deserializer and found that the CML low-to-high and high-to-low transition times are out of spec. The transition times in my system are just under 1nS.

1. Would there be any negative effects from this? (bit errors?)

2. The SER and DES are connected through a CAT5e cable, the standard cable used is 3m and changing to a very short cable (2 feet) does not have any effect on the transition time. What are my other options to increase the transition times of the diff pair?

Thanks.

Brad.