Hi,

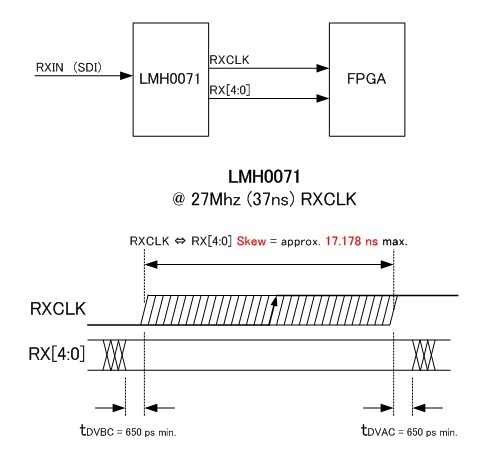

I would like to know if my undertanding is correct about the RX[4:0] Data Valid after/before clock (tDVBC, tDVAC) of LMH0071 Deserializer. In the datasheet the minimum tDVBC and tDVAC is 650 ps, but LMH0071 clock is only 27Mhz or 37 ns. Divide this by 2 due to the DDR clocking and the data period is 18.7 ns. This would make the tDVBC and tDVAC minimum to around 9 ns. Am I right with this?

<Documents>

Datasheet : http://www.ti.com/lit/ds/symlink/lmh0071.pdf

LVDS Timing overview : http://www.ti.com/lit/an/snla122a/snla122a.pdf

Best Regards,

Celmar