I am looking for assistance in troubleshooting an I2C issue with my circuit.

I am using the DS92LX2121/DS92LX2122 in display mode. The DS92LX2121 (Serializer) is connected to my main processor and set to mode 1. The deserializer is set to mode 0.

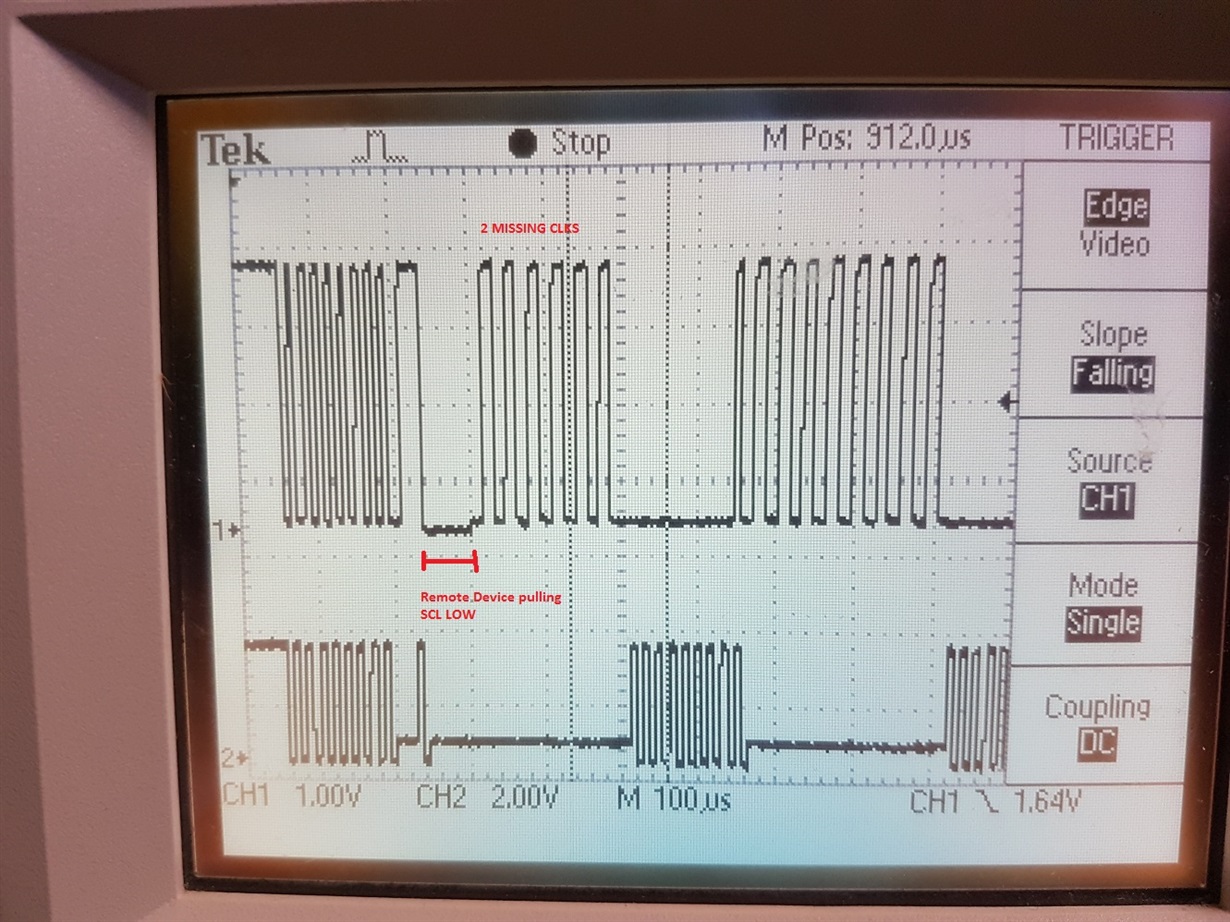

It seems that the deserializer does not support SCL clock stretching when initiated by the connected remote device. This is evident because I only see 5 clocks being output by the deserializer when performing a read. When I slow down the deserializer i2C read rate to 11KHz (Register 6), I can see all 8 clock pulses and get valid/in-sync data.

The three missing clocks in the first example are the first bits of the byte and are seem to occur when the remote device is pulling SCL low. The remote device pulls SCL low for about 70us.

The remote device pulls SCL low after the slave address read is acknowledged but before a clock pulse is output by the deserializer.

All my other I2C devices work fine. This could be due to the fact that none of the other device clock stretch.

My question is.... Does the deserializer support clock stretching by the connected remote slave devices? If it does, what could I do to fix it?

Thank you