The LMH0044 datasheet states that it can equalize up to 200 meters of Belden 1694A at 1.485 Gbps. The jitter for various cable lengths (with equalizer pathological) are stated a table.

At 140 meters of Belden 1694A cable, the typical jitter is 0.25 UI. At 200 meters of the same cable, the typical jitter is 0.30 UI. This is the output timing jitter right?

Since 200 meters - 140 meters = 60 meters and 0.30 UI - 0.25 UI = 0.05 UI, every 60 meters of Belden 1694A cable has roughly 0.05 UI of jitter?

Thus, 200 meters of cable has: 200 meters / 60 meters = 3.33 * 0.05 UI Jitter = 0.17 UI Jitter.

Thus, the rest, 0.30 UI - 0.17 UI = 0.13 UI jitter is intrinsic to the device?

Since SMPTE 292 specs the max timing jitter as 1 UI, jitter is not the limiting factor preventing the device from equalizing Belden 1694A cable longer than 200m. is the limiting factor the losses in the cable and the device's equalization ability. What is the maximum jitter the input of the LMH0044 can tolerate? Will the output jitter remain the same?

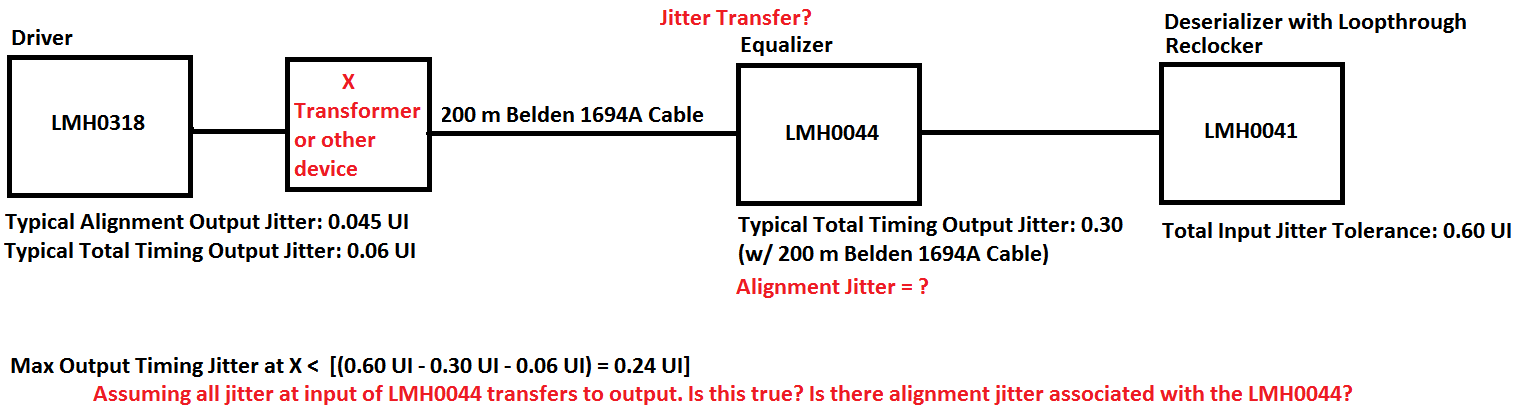

The link is shown below. I am looking to understand the jitter budget of my system, which entails understanding the jitter transfer and alignment of the LMH0044. We are neglecting jitter associated with other unlisted cables, connectors, and PWB traces. I'm looking at understanding how much jitter budget I have left in the system for a transformer or other device (X in figure below).

Could you help me understand? Also, does the reclocker eliminate all the alignment jitter?