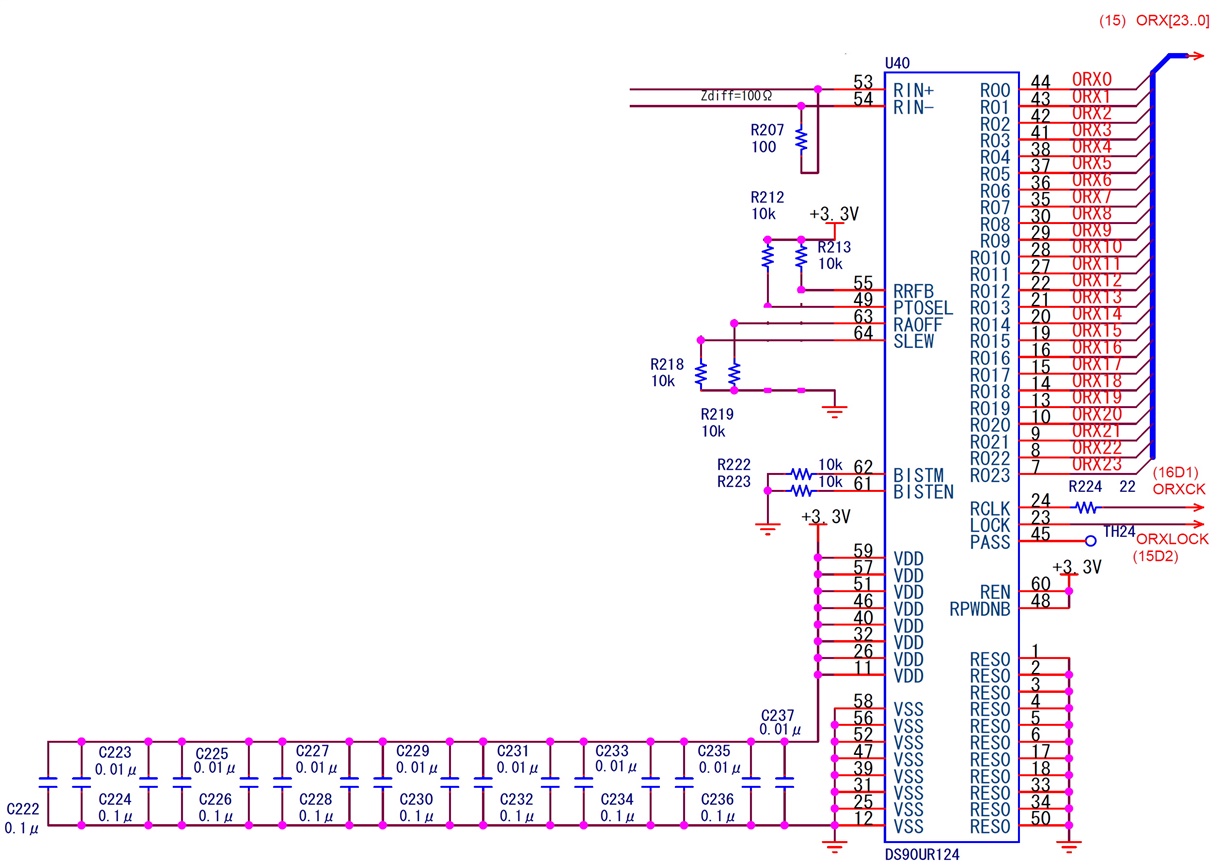

The DS90UR124 is used for communication, but there are some cases where there is no input signal.

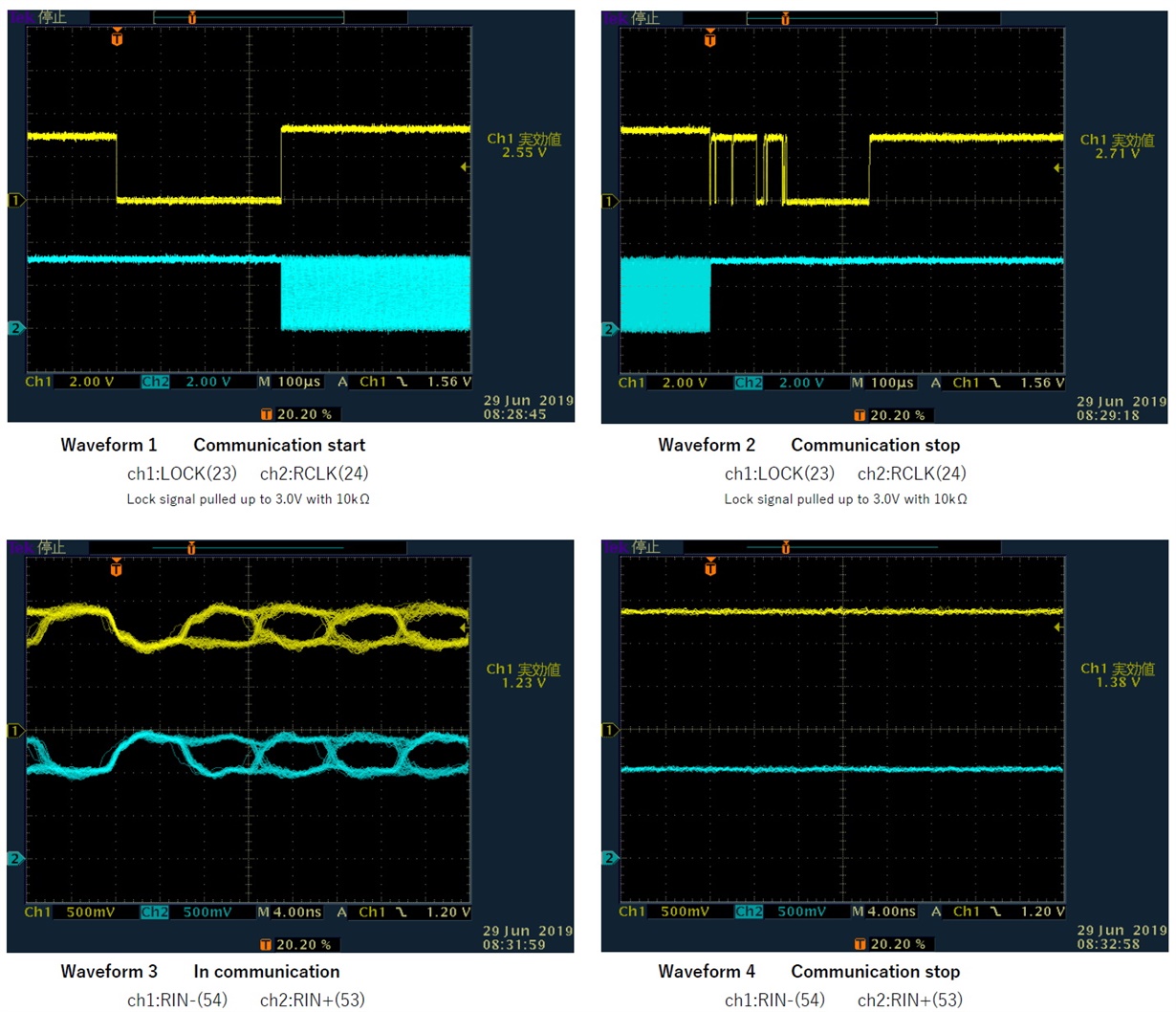

When there is no signal in the input of RIN+ and RIN-, I thought that the output of the LOCK signal is L level, but it seems to be Hi-Z.

There is a description of "Also, the Deserializer LOCK output will remain low until its PLL locks to incoming data and sync-pattern on the RIN± pins." on page 19 of the data sheet.

The signal settings are fixed to RPWDNB=H, REN=H, and RAOFF=L.

Table 2 on page 23 of the datasheet shows LOCK=H when PLL is locked, and LOCK=L when not locked.

I thought the lock signal output was L-level, even if there was no signal on the RIN+ and RIN- inputs, just as if the PLL was not locked, but the LOCK output is Hi-Z.

Is it correct that the LOCK output will be Hi-Z when there is no signal in the RIN+ and RIN- inputs when not in power-down mode?