Other Parts Discussed in Thread: SN65LVELT23, SN65EPT23, SN65EPT22

Hello support team,

I have some questions about SN65LVELT22 and SN65LVELT23.

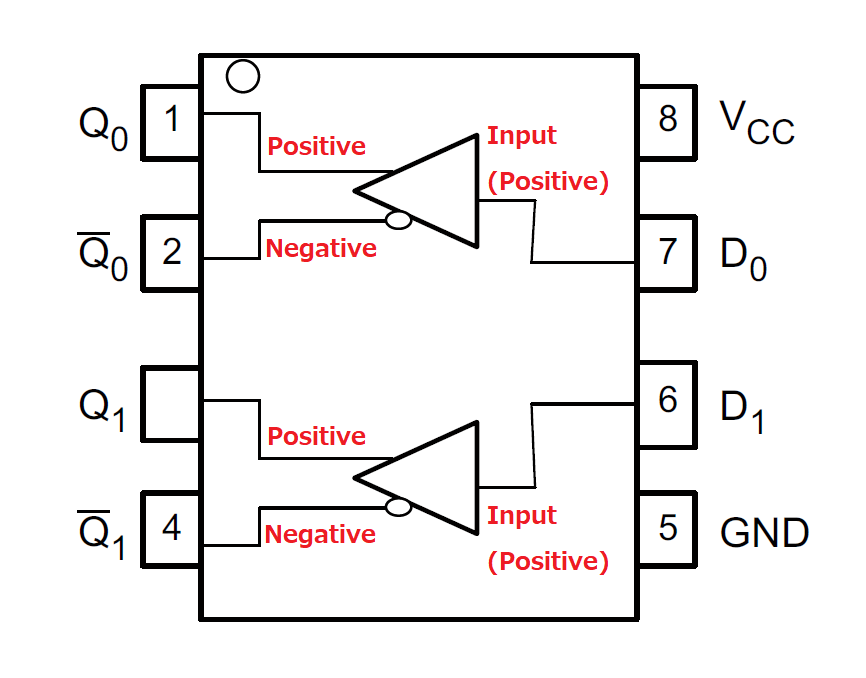

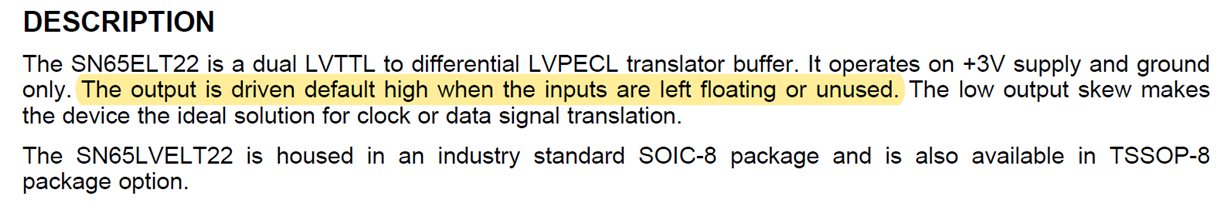

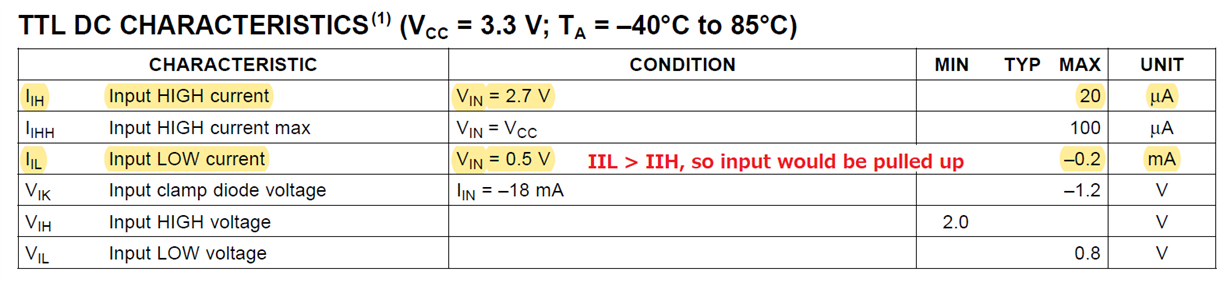

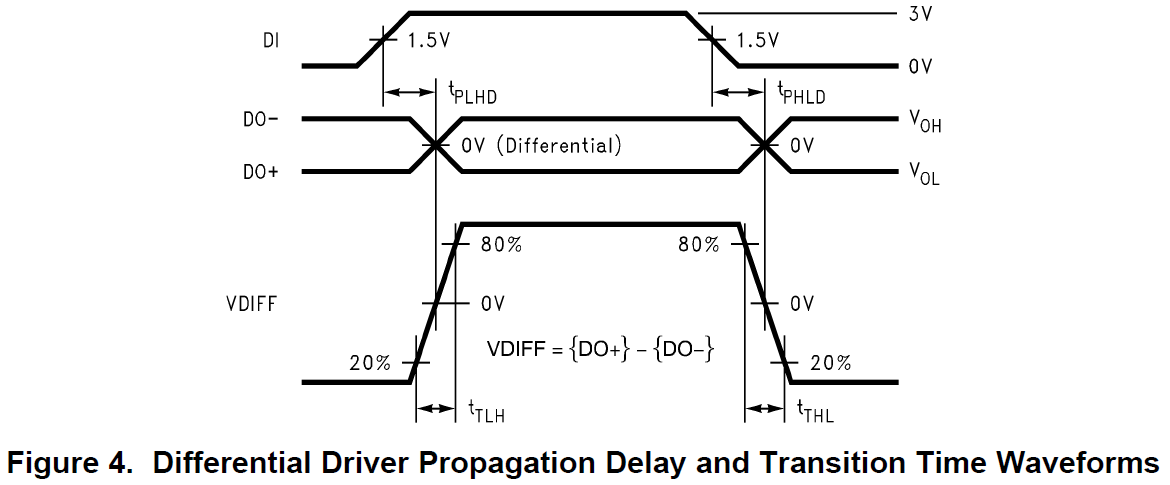

Regarding SN65LVELT22, Figures 2 and 4 on pages 4 and 5 of the datasheet provide time charts for input and output signals.

These don't match the signal polarity of block diagram described on page 1 of the datasheet.

Perhaps I think the polarity of the output signals shown in Figure 2 and Figure 4 are reversed.

Also regarding SN65LVELT23, I think the polarity of the output is reversed in Figure 3 of the datasheet.

Is my understanding wrong?

Sincerely,

M. Tachibana