Other Parts Discussed in Thread: AM26LS31

Hello

I have a question in a block diagram.

Please may I explain in detail.

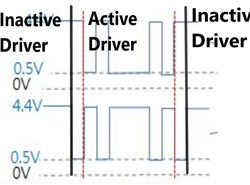

Q1> Are there any problems with UART connection due to the differential line receiver (SN75157) interface and electrical characteristics in [Fig 2]?

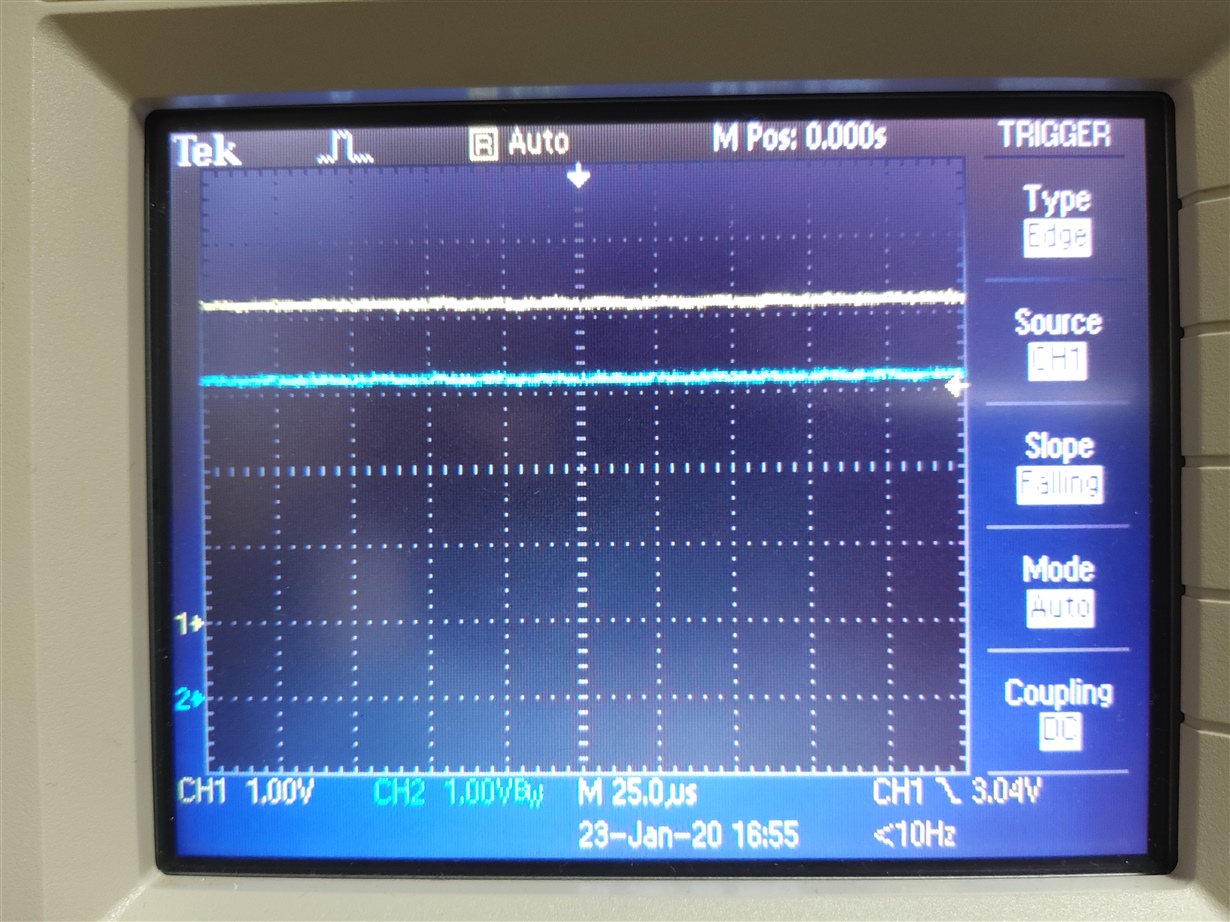

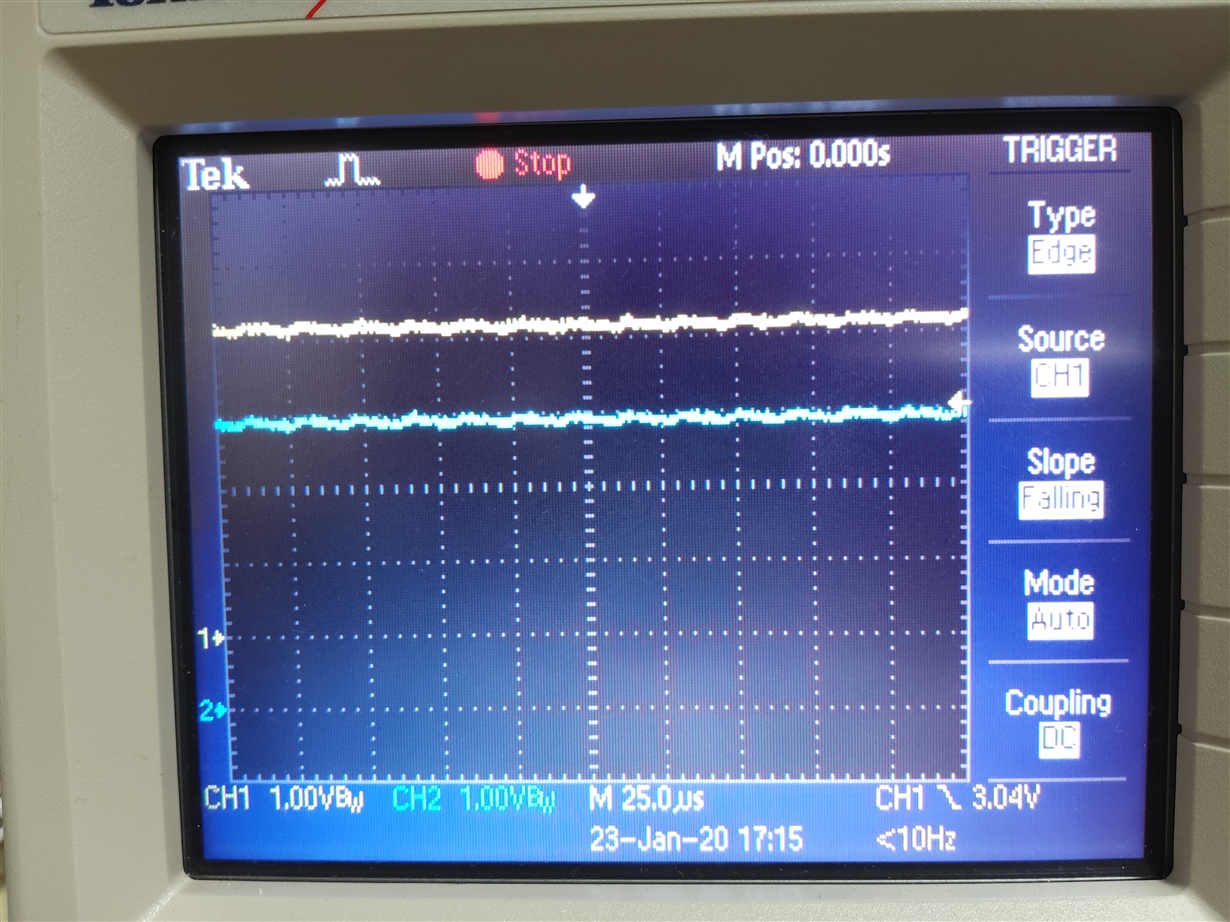

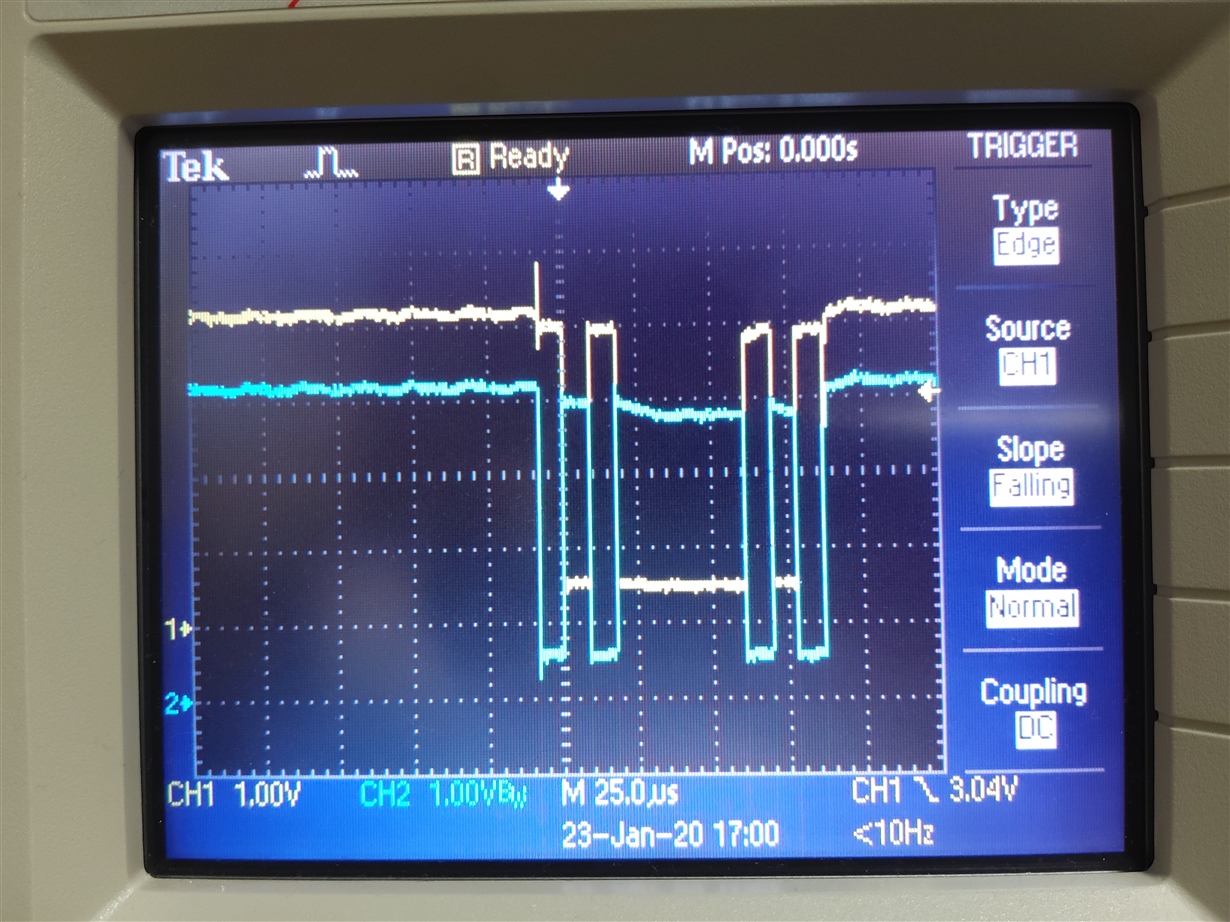

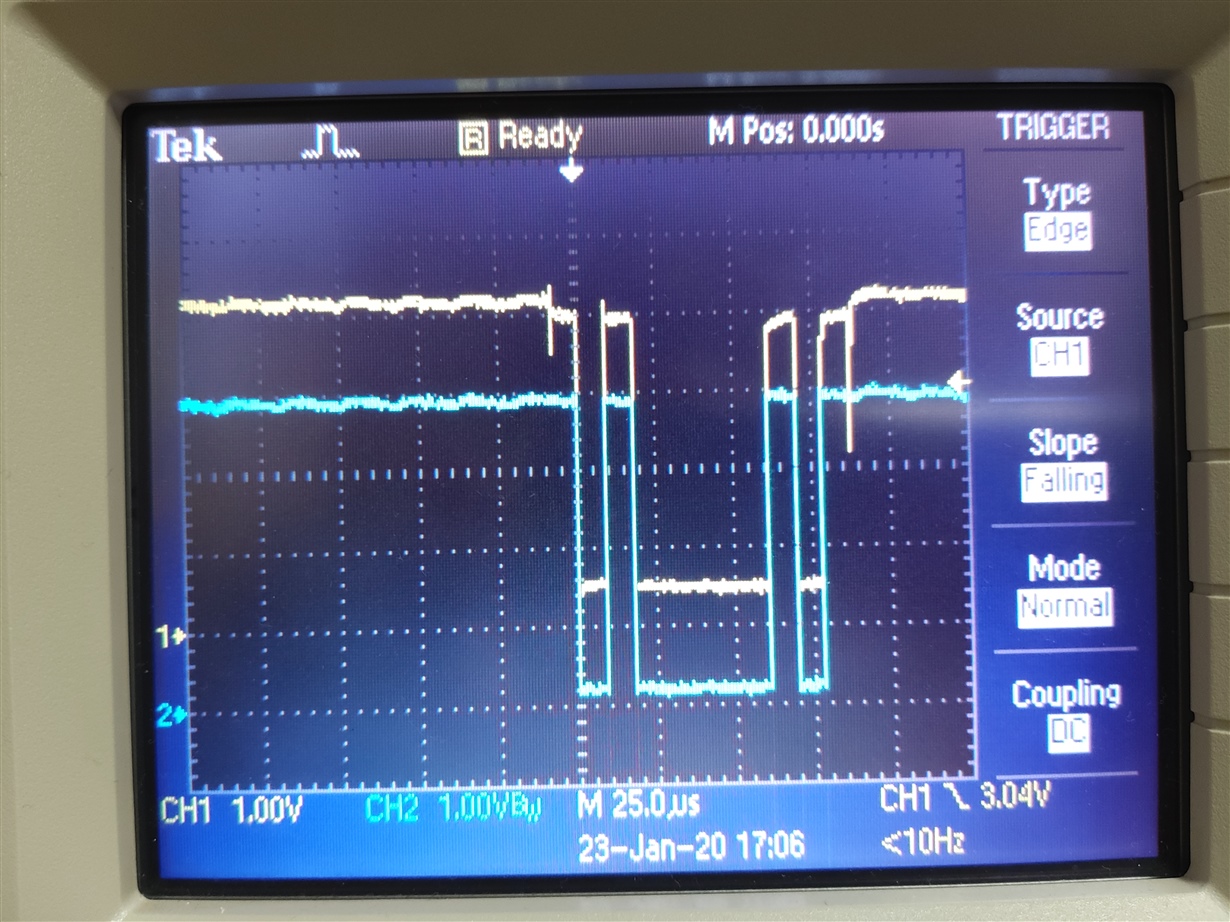

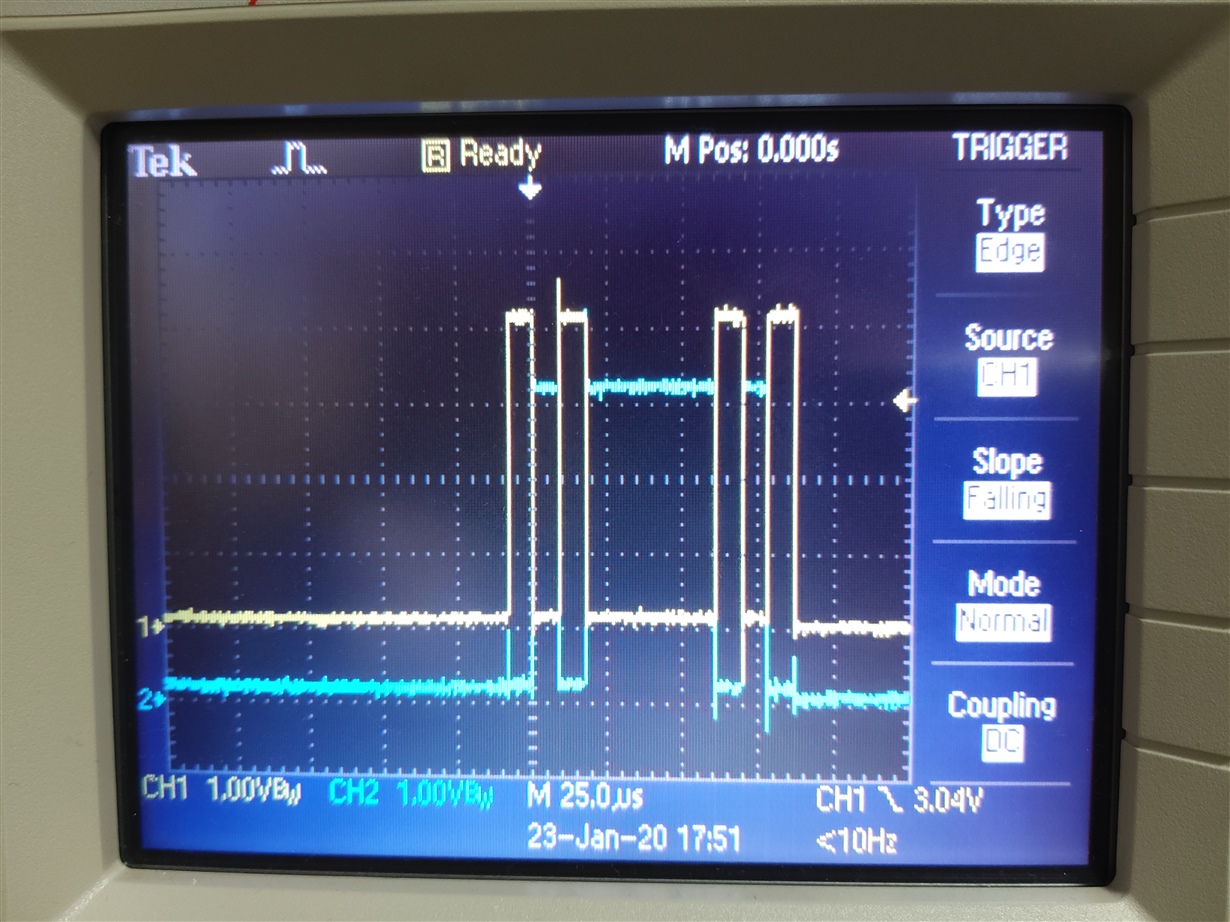

Q2> [Fig 4] is output signal of Differential Line Receiver (AM26LS32ACPW) IC of [Fig 1].

Sometimes the reference potential starts from above. Or the reference potential starts from below.

I don't know why. Is this the problem with the device (AM26LS32ACPW)?

Q2-1> Also, Is there a problem with the differential line receiver (SN75157)?

Q3> Is there any problem with the resistance value of Rt 120ohm and the electrical characteristics of the slave in [Fig 2]?

Q4> Are the output waveforms of the SN75157 input signals IN + (A-out) and IN- (A + out) in [Fig 2] correct?

Best Regards,

Jame,Shin