Other Parts Discussed in Thread: LV24EVK01

Hi Professional,

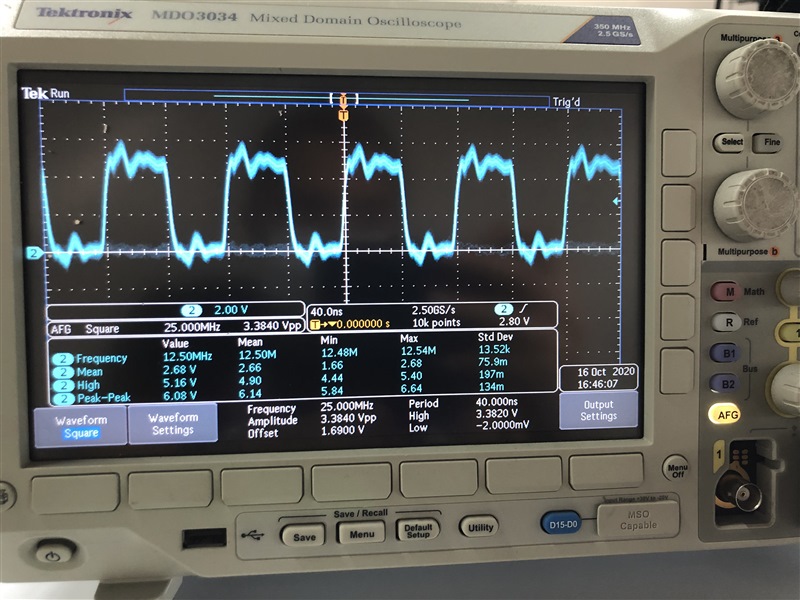

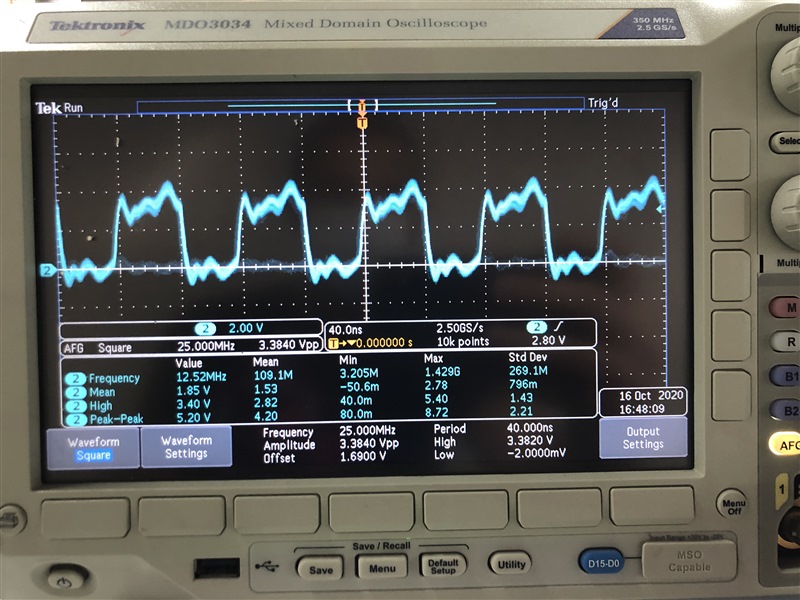

I am currently trying to use ser / des (LV24EVK01) implementation on a certain video panel application.I give the input clock (25 MHz) signal of serializer from FPGA. But the LOCK and PASS pin of the deserializer are not going high. It doesn't work with the signal which is posted below. I tried giving some other signals as clock source from some other sources and they worked well. I am awere the input pins of the ser / des pair accepts max 3.3V, some other oscilloscope generated 5V 10MHz clock signal worked as well. I am uploading 2 signals which are generated from FPGA, one of them is 5V and other one is 3.3V. Could you enlighten me out what could be possibly wrong in my situtation?