Other Parts Discussed in Thread: DSI-TUNER,

Hi Tis,

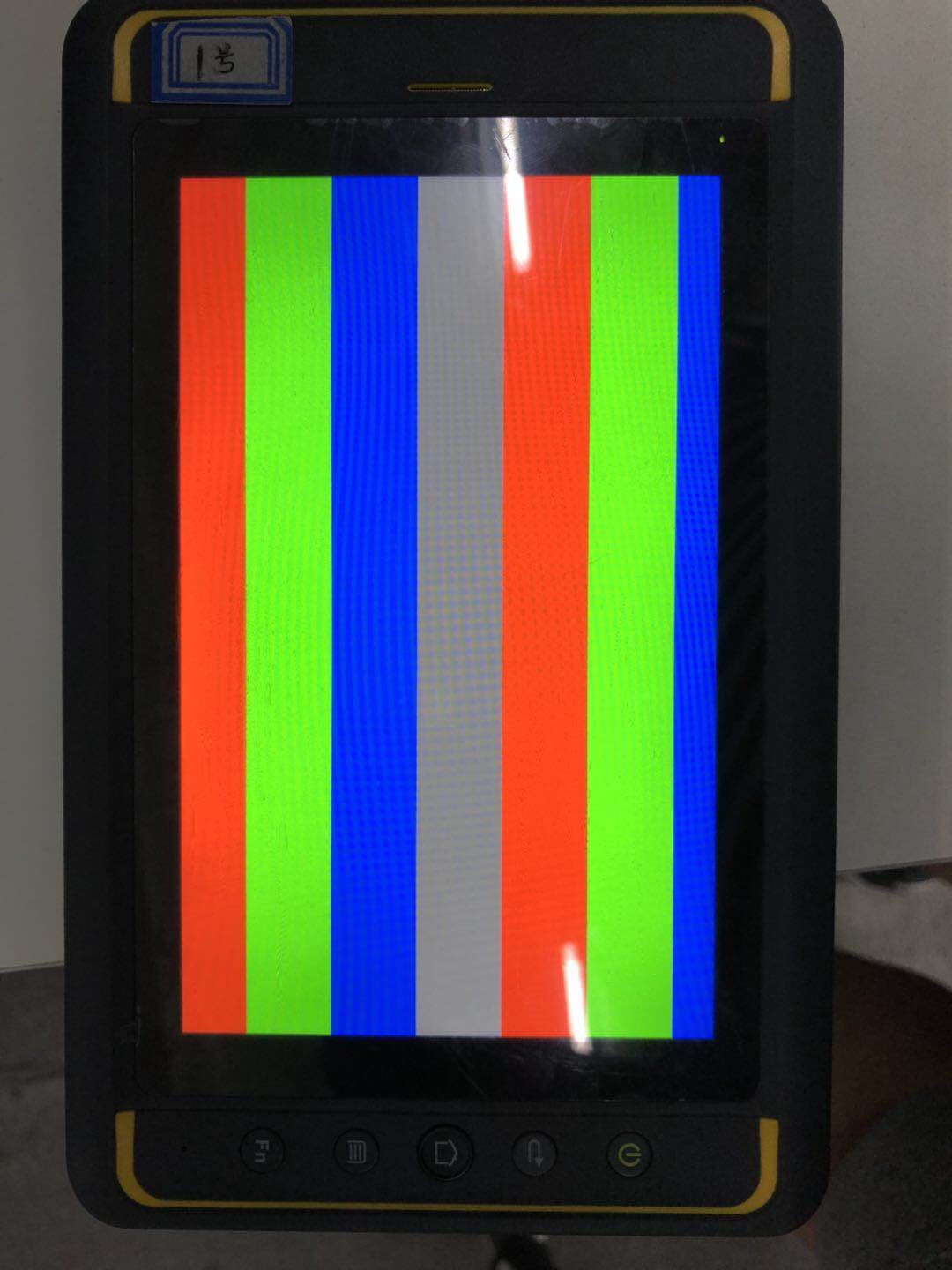

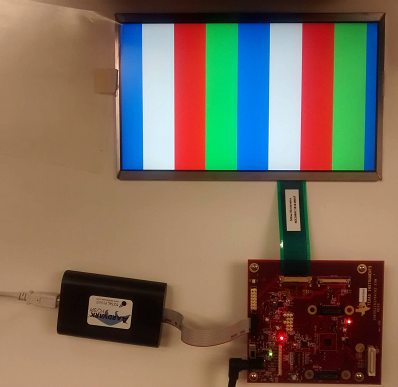

My Ctm had used the SN65DSI83 as mpi to lvds bridge.,LCD driver ic is LQ070K1LX80. In gray screen, there is a remnant.

Would you pls give me some advice?

the code is as follow:

#define SN65DSI83_BUSNUM 3

static struct i2c_board_info __initdata i2c_sn65dsi83 = { I2C_BOARD_INFO("sn65dsi83", (sn65dsi83_SLAVE_ADDR_WRITE_MOUDLE>>1))};

static int __init sn65dsi83_init(void)

{

printk("[sn65dsi83_init] init start\n");

i2c_register_board_info(SN65DSI83_BUSNUM, &i2c_sn65dsi83, 1);

if(i2c_add_driver(&sn65dsi83_driver)!=0)

{

printk("[sn65dsi83_init] failed to register sn65dsi83 i2c driver.\n");

}

else

{

printk("[sn65dsi83_init] Success to register sn65dsi83 i2c driver.\n");

}

return 0;

}