Part Number: DP83867IS

Hi,

With respect to 10BASE-Te in TI dp83867IS phy chip, I have a few questions.

First, I would like to know if the setting of the sleep mode or wake_on_lan function in the dp83867 affects the receive packet frame.

These functions seem to be disabled by default, but I would like to know if the setting of the above functions affects the operation of 10 BASE-Te and the state change of recive packet.

When we compare the voltage difference with the equipment using other phy chip in 10Mbps communication state, we can not find any difference.

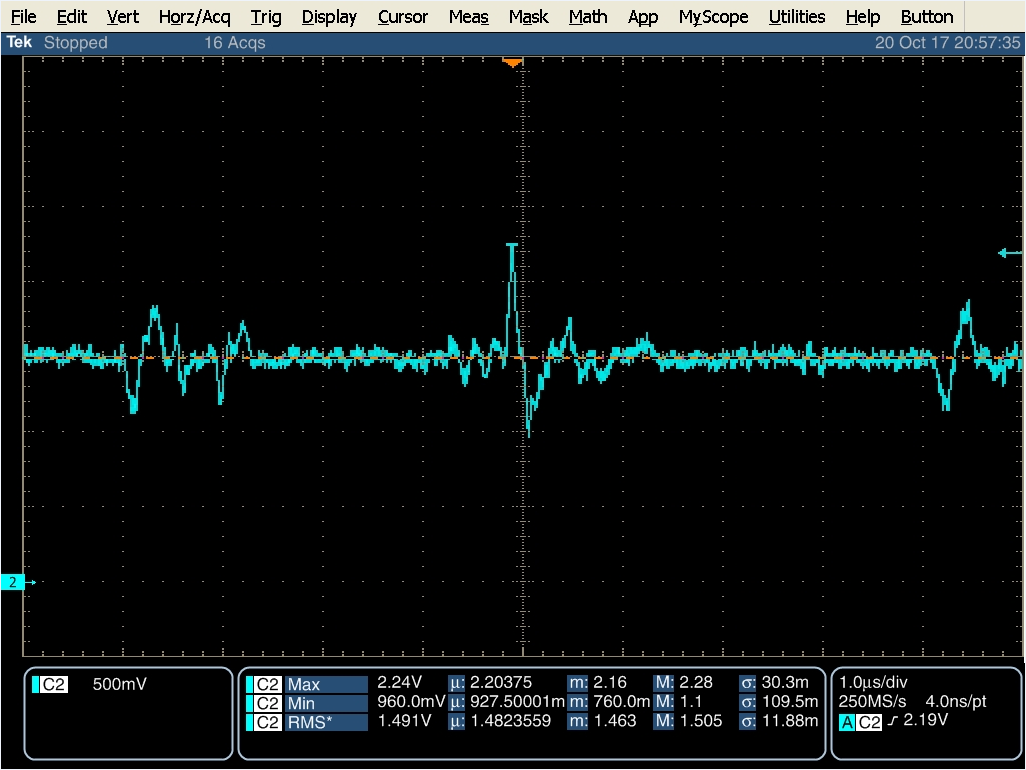

1. Equipment used DP83867

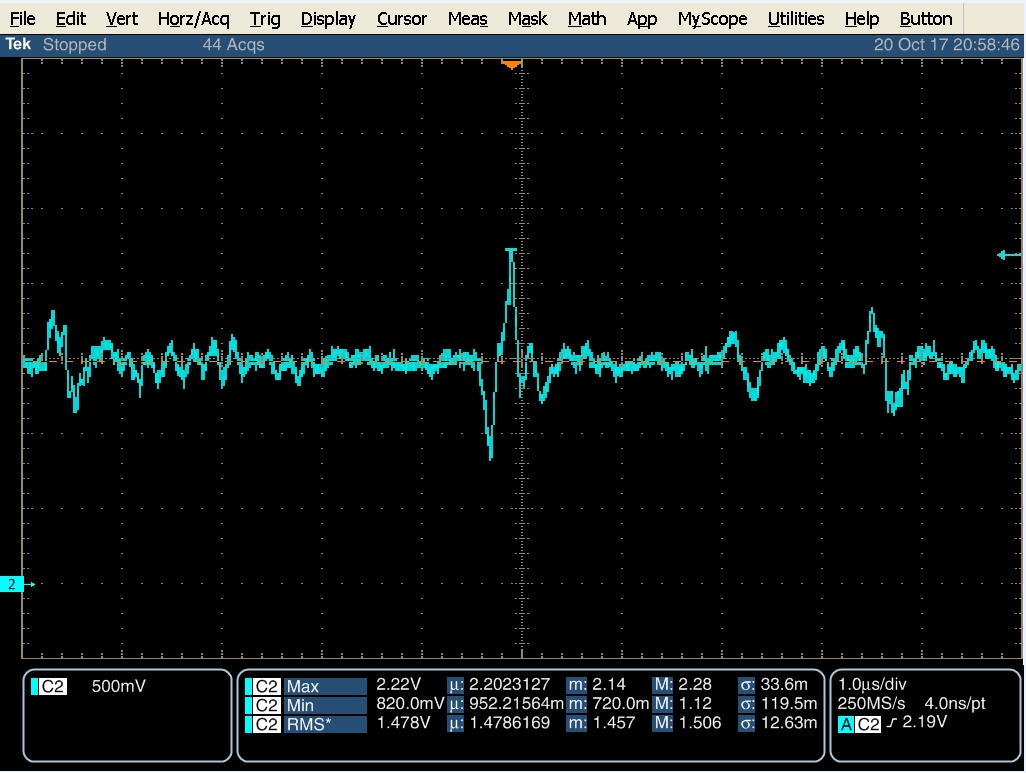

2. Equipment used other vendor phy chip

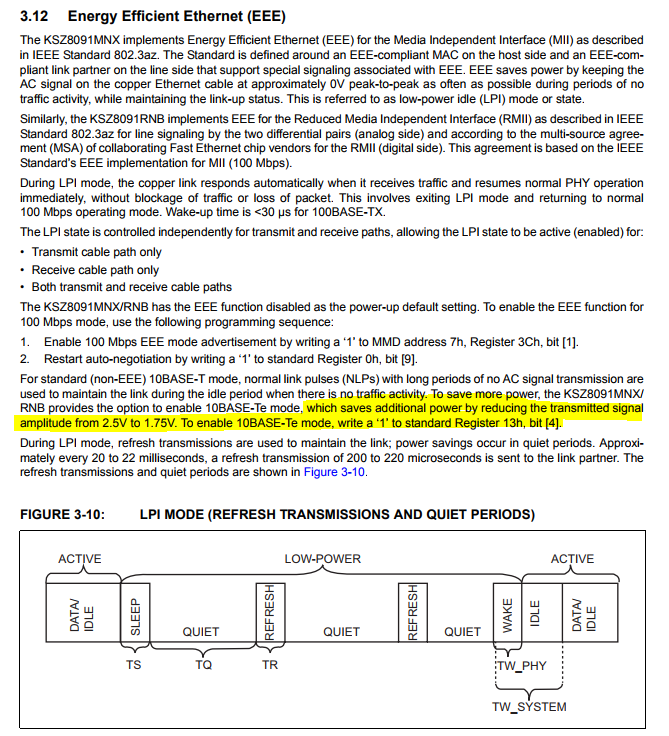

Second, I would like to know if there is a capability to change 10BASE-Te to 10BASE-T in dp83867.

While investigating 10BASE-Te, some other vendor's phy chips support 10BASE-T while changing to 10BASE-Te, so I would like to know if the dp83867 has this function.

(below is from page 33 of http://ww1.microchip.com/downloads/en/DeviceDoc/00002275A.pdf )

thanks,

TS