Hi,

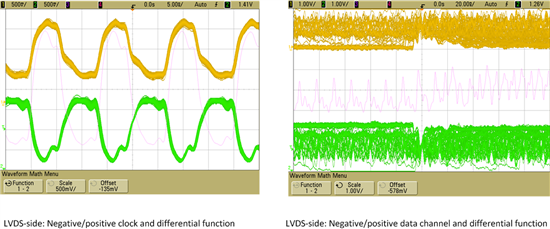

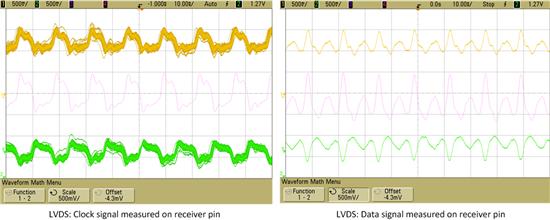

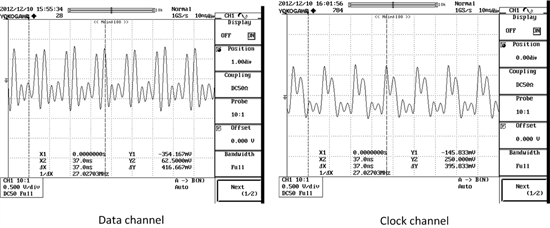

I developed a DVI to LVDS bridge for an optical measurement system. Last week I got my first prototype, unfortunately I have a huge problem with jitter on the most of the LVDS lanes coming from DS90C387A. For my pcb design, I followed the rules from "LVDS Owner Manual" and calculated the vaules for my pcb traces. But it seems that I have done something wrong. See the next picture:

Left pictures shows my differential output clock on the end of my cable (before it goes to my lcd panel). Clock looks not so bad, but may data channel is realy horrible. And so my panel shows only a really noisy image. One thing which could cause this jitter could be my to connectors which I have soldered:

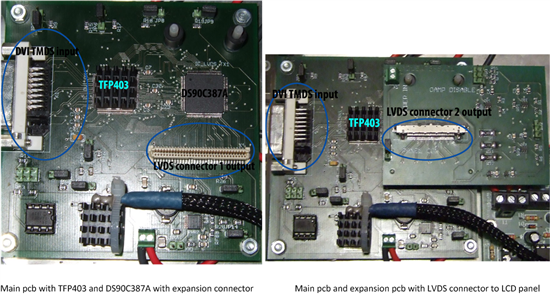

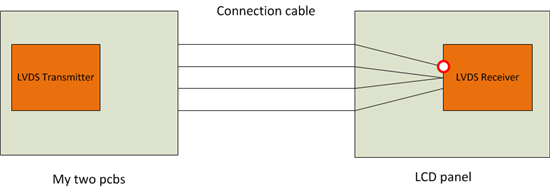

Here you can see my pcb, left pictures shows my frist pcb connector where the LVDS signals will go to my second pcb. From there (right picture) the signal will follow from LVDS connector 2 to lcd panel via cable (length about 20 cm).

Has anybody perhaps some suggestions for improving my signal? I looked for some LVDS repeater/buffer and I found DS25BR100 and DS25BR440. Could they help me to reach my goal?

I'd appreciated if somebody could help me.

Best regards

Jürgen