Other Parts Discussed in Thread: DP83640

AC coupled link between DP83640 PHY does not work with Micrel Ethernet Switch which has internal bias and termination.

When transformerless connection, using 0.1uF/0603/X7R capacitors and 50 Ohms termination resistors to 3.3V on PHY side is used, link is established and stable at 100Mb/FD, PHY receive pair operates fine, but in transmit direction no packets are received by a link partner.

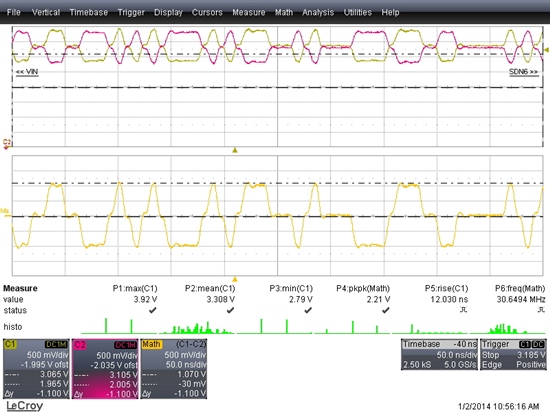

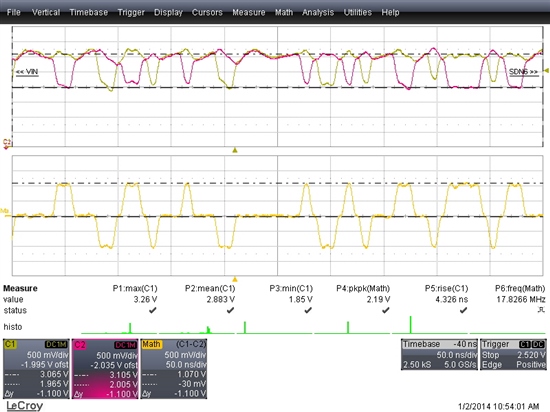

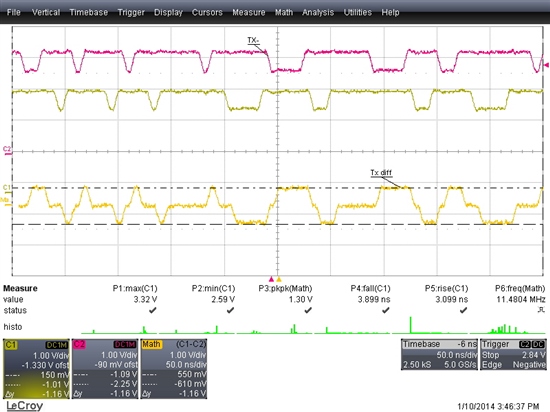

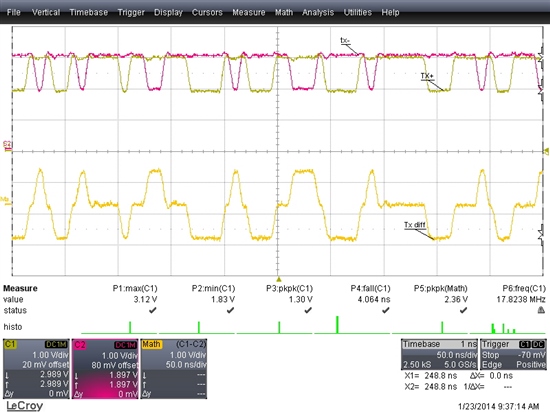

Apparently Micrel Ethernet Switch does not receive 2-level (single ended) pattern coming from DP83640, no packets are received, while link is established and steady at 100Mb/FD or HD. Differential signal looks OK, but single ended waveform does not look like MLT-3.

When link speed is set to 10Mb, ot through magnetics, link operates fine in both directions.

When output signal from DP83640 is attenuated (using 18Ohms termination instead of 50Ohms) link starts to operate at 100Mb, but not on all boards, on some boards with DP83640 link starts dropping, becomes unstable

Same Micrel Switch works fine in both directions when other (non-TI) PHY is used, AC coupled same way, but in that case MLT-3 waveform from/to PHY is both single ended and differential.