Hi Team,

My customer has 2 questions regarding MIDO, could you follow these questions below?

1. Pull-up registers

2.2kohm pull-up register are used on MDIO line though, can they change it to 1kohm?

According to My customer, They have seen bad waveform like below at MDIO lines (TLK10232 to FPGA) on their board. It looks like low pass filter was applied(There may be a relatively large parasitic capacitance on the lines).

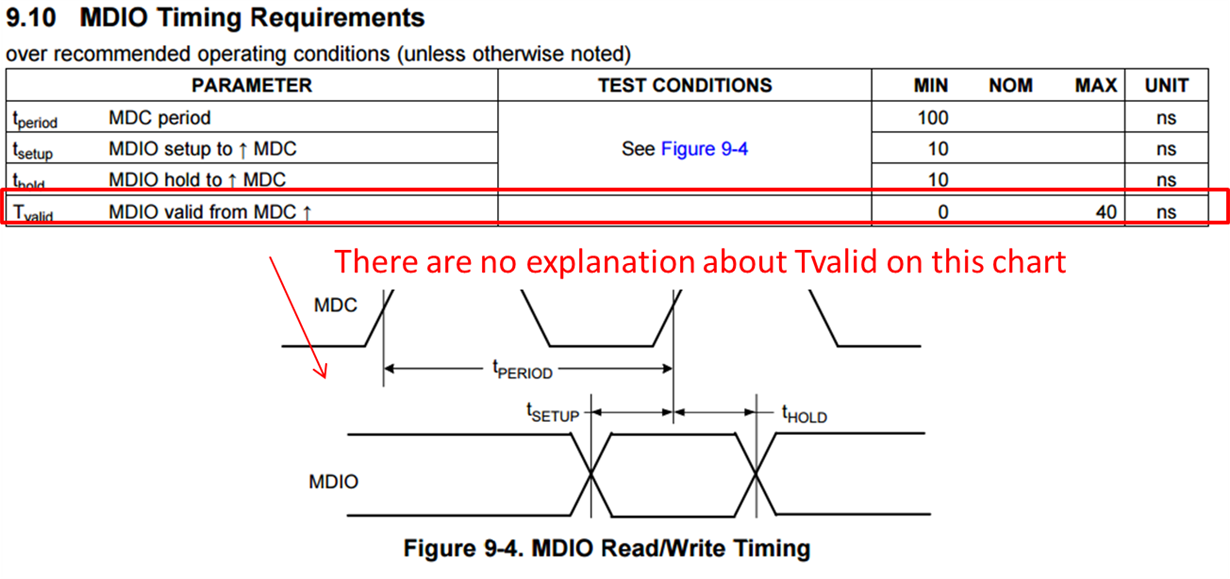

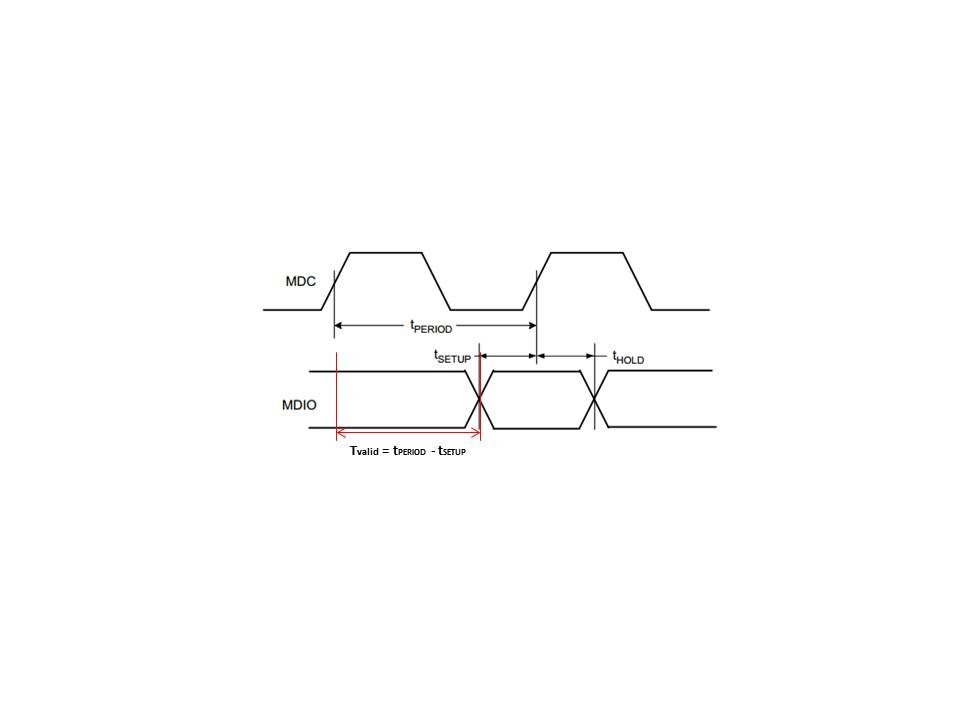

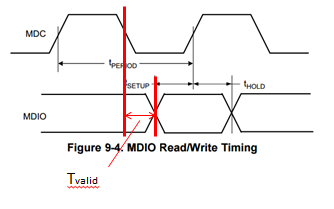

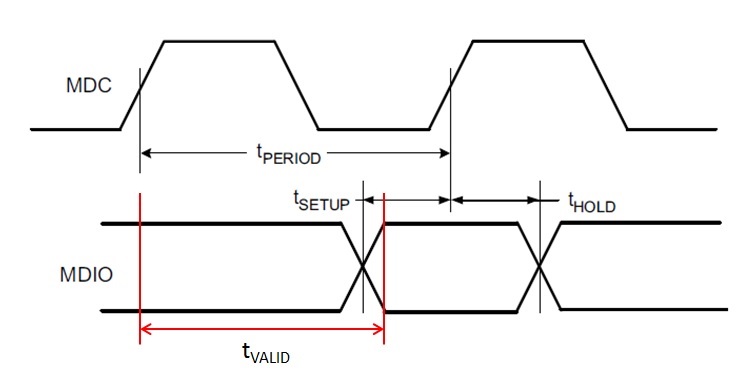

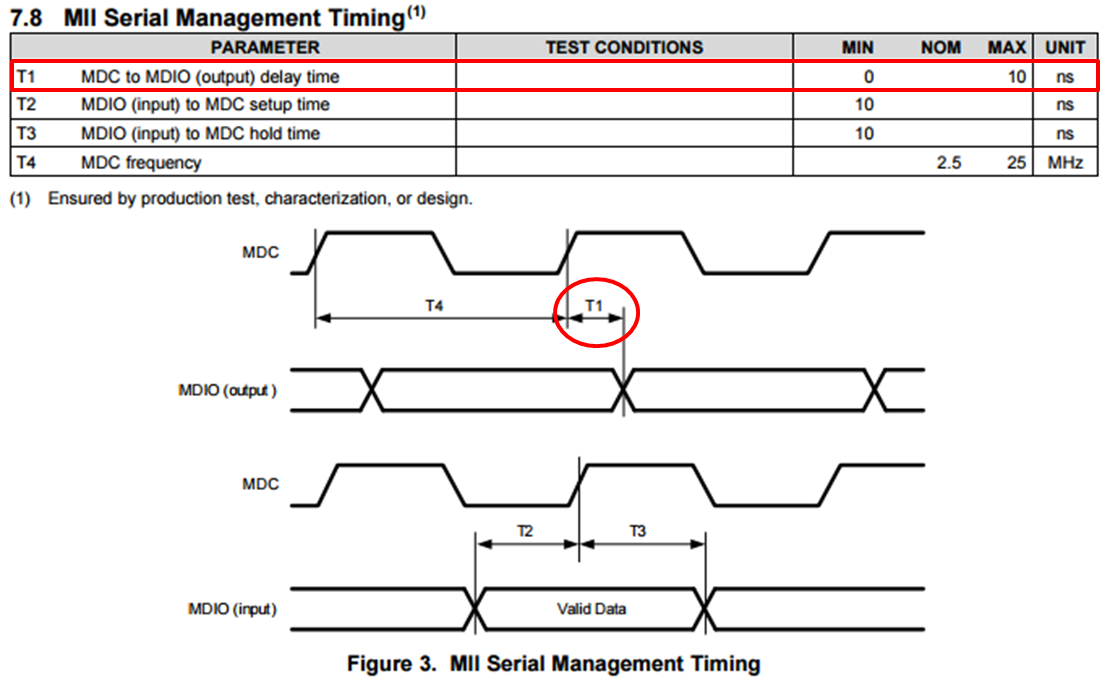

2. Meaning of Tvalid indicated in 9.10 MDIO Timing Requirements

My customer want to know what Tvalid means, could you tell me that with a timing chart like Figure 9-4. MDIO Read/Write Timing?

Regards,

Takashi Onawa