Other Parts Discussed in Thread: TPS2547, , TPS2549

Hi

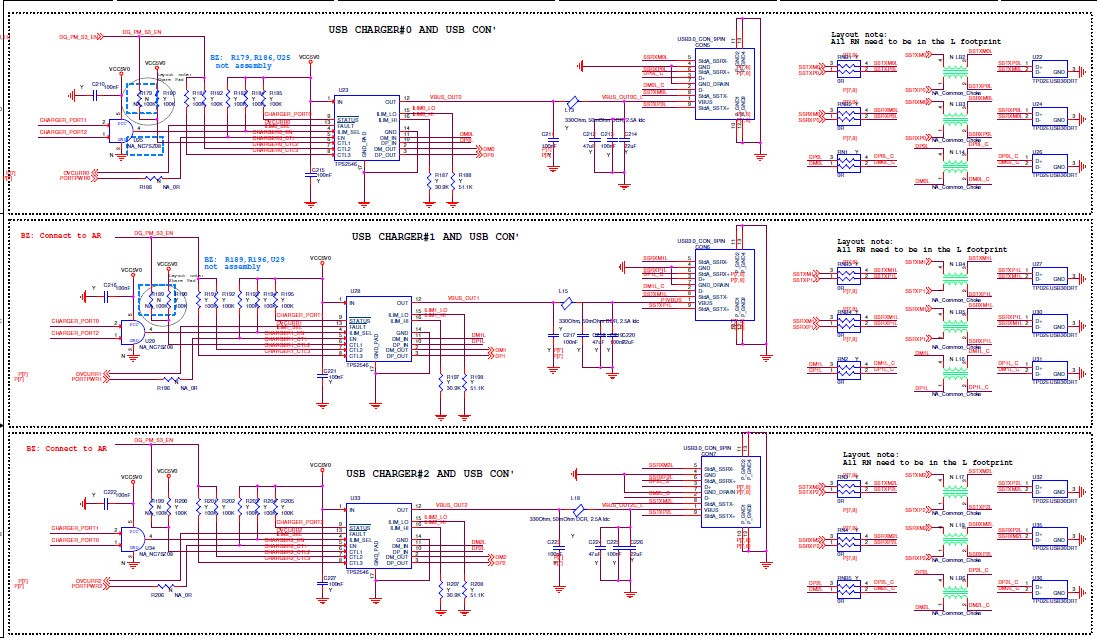

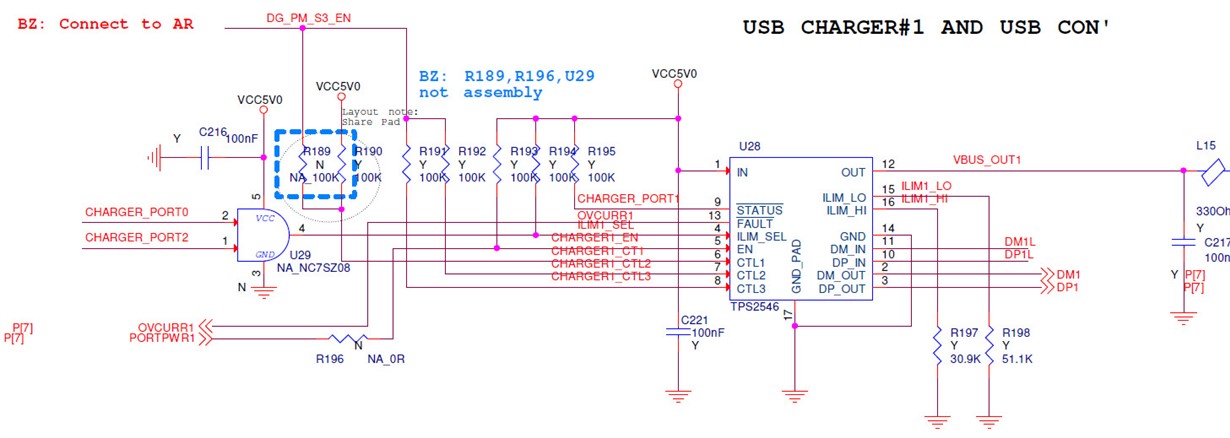

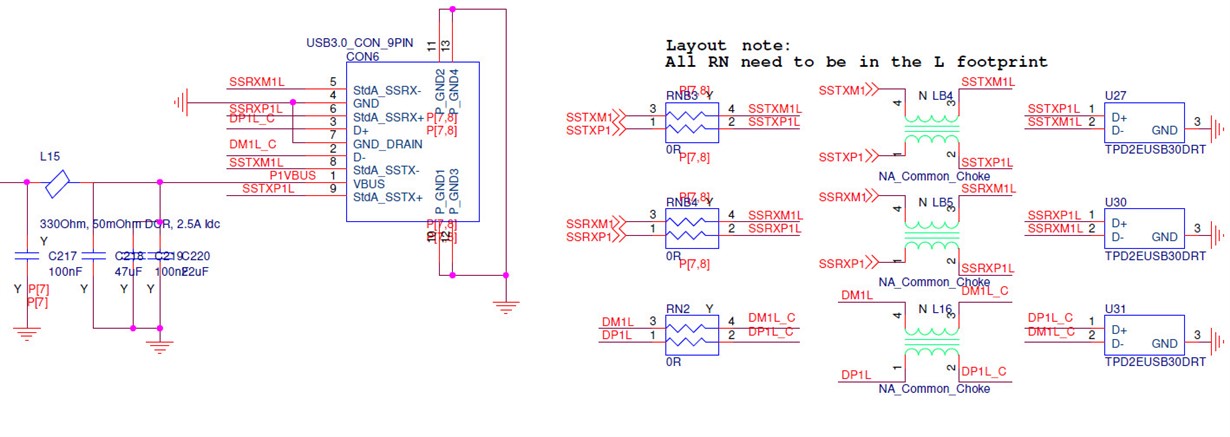

My customer used TPS2546 can not pass the USB certification. We got fail about A4.9: Host Test J/K, SE0_NAK (EL_9) in SDP / CDP mode.

SDP mode Test K in D+ is over 20mV and D- is pass. CDP mode Test J in D- is over 20mV and D+ is pass. Do you have any suggestions? Thanks for help~